Ingenieurhochschule fuer Seefahrt

Warnemuende/Wustrow

Abteilung Rechentechnik und

wissenschaftlicher Geraetebau

\*\*\*\*\*

\*

\* NANOS

\* Floppy-Disk-Interface Baugruppe

\* : R 233 -101 / 11.0

\*\*\*\*\*

Bearbeitung:

H. Nergen

Warnemuende; den 30.04. 1987

R 233 - 101/11.0

## Inhaltsverzeichnis

Seite

|         |                                                           |    |

|---------|-----------------------------------------------------------|----|

| 1.      | Kurzcharakteristik                                        | 4  |

| 2.      | Technische Daten                                          | 5  |

| 3.      | Funktionsbeschreibung                                     | 6  |

| 3.1     | Funktionsgruppen                                          | 7  |

| 3.1.1   | Busankopplung                                             | 7  |

| 3.1.1.1 | Adress- und Steuersignaldecodierung                       | 7  |

| 3.1.1.2 | Baugruppenadressierung                                    | 9  |

| 3.1.2   | Laufwerkfunktionsregister                                 | 9  |

| 3.1.3   | Floppy-Disk-Controller U 8272                             | 11 |

| 3.1.4   | Schreibsteuerung                                          | 15 |

| 3.1.4.1 | Takterzeugung                                             | 15 |

| 3.1.4.2 | Schreibtaktgenerierung WRCLK                              | 15 |

| 3.1.4.3 | Praecompensation der Schreibdaten                         | 16 |

| 3.1.5   | Lesesteuerung - Datenseparator                            | 17 |

| 3.1.5.1 | Wirkungsweise der PLL                                     | 18 |

| 3.1.5.2 | Schaltungsbeschreibung                                    | 19 |

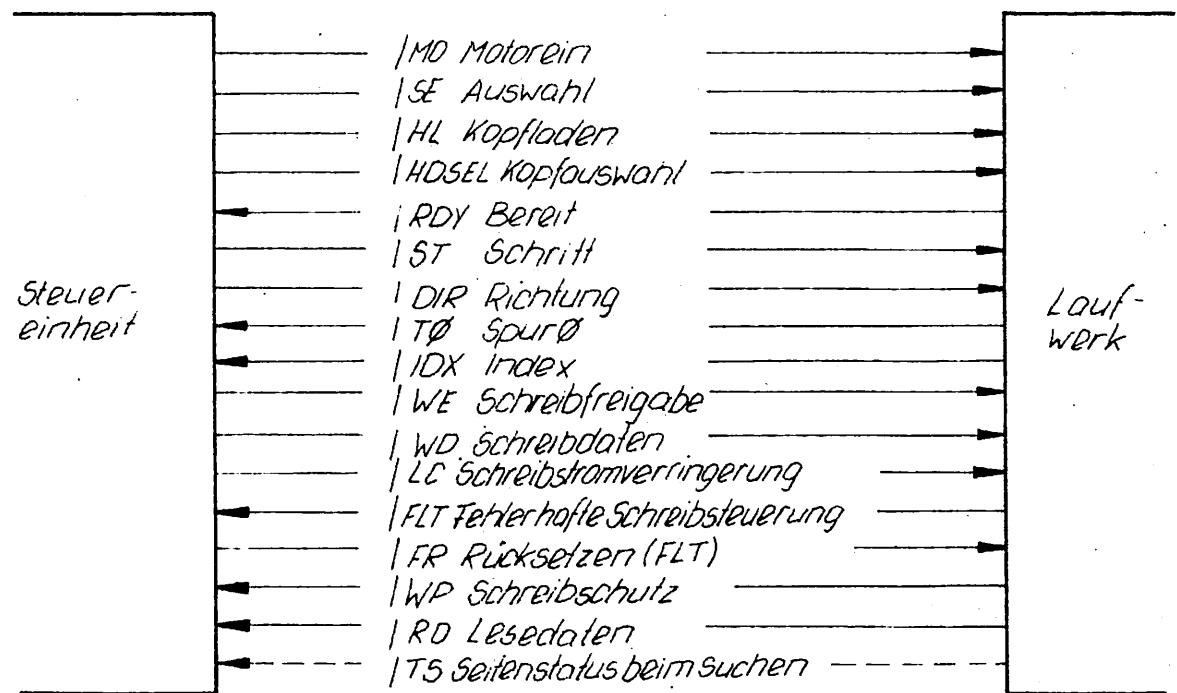

| 3.1.6   | Peripherieankopplung                                      | 20 |

| 3.1.7   | Transverter                                               | 21 |

| 3.2     | Anschlussbedingungen                                      | 22 |

| 3.2.1   | Systembusankopplung                                       | 22 |

| 3.2.2   | Interfaceanschluss FD-Laufwerke                           | 22 |

| 4.      | Inbetriebnahme und Pruefung                               | 23 |

| 4.1     | Vorpruefung der unbestueckten Leiterplatte                | 23 |

| 4.2     | Bestueckungs- und Inbetriebnahmehinweise                  | 23 |

| 4.2.1   | Aufbau und Pruefung des Transverters                      | 23 |

| 4.2.2   | Aufbau und Pruefung des Datenseparators                   | 24 |

| 4.3     | Pruefung und Inbetriebnahme der bestueckten Steckleinheit | 25 |

| 4.3.1   | Pruefung der bestueckten Baugruppe                        | 25 |

| 4.3.2   | Stromaufnahme der Baugruppe                               | 26 |

| 4.4     | Erstinbetriebnahme                                        | 26 |

| 4.5     | Pruefprogramm                                             | 28 |

| 5.      | Anwenderhinweise                                          | 30 |

| 6.      | Anlagen                                                   |    |

7. Konstruktionsunterlagen

|                        |                                                            |

|------------------------|------------------------------------------------------------|

| Uebersichtsplan        | R 233-101/11.0 Uep(3) Bl.1                                 |

| Projektierungssymbol   | R 233-101/11.0 Ps (4) Bl.1                                 |

| Funktionsgruppenplan   | R 233-101/11.0 Fp (4) Bl.1                                 |

| Stromlaufplan          | R 233-101/11.0 Sp (3) Bl.6<br>R 233-101/11.0 Sp (4) Bl.1-9 |

| Leiterbildzeichnung LS | R 233-101/11.0 LBL(4) Bl.1                                 |

| Leiterbildzeichnung BS | R 233-101/11.0 LBB(4) Bl.1                                 |

| Schaltteilliste        | R 233-101/11.0 SL (4) Bl.1-6                               |

| Bestueckungsplan       | R 233-101/11.0 Bsp(2) Bl.1                                 |

## 1. Kurzcharakteristik

Die Floppy-Disk-Anschluszeuereinheit (FDCI) ist ein Modul des NANOS-Baugruppensystems im Format 95 mm x 170 mm. Sie ermöglicht den Einsatz von Floppy-Disk-Speichern, die als Standardmassenspeicher in Mikrorechnersystemen zur Anwendung kommen.

Grundbaustein der FD-Ansteuereinheit ist der Floppy-Disk-Controller U 8272, der die logischen und verwaltungstechnischen Aufgaben der Baugruppe ausführt.

Sie gestattet den Anschluss von 5 1/4- und 8-Zoll-FD-Laufwerken (MINI-/STANDARD-LW) an den K 1520-Systembus.

Die Aufzeichnung der Daten erfolgt mit dem modifizierten Frequenzmodulationsverfahren MFM (doppelte Schreibdichte) bzw. dem FM-Verfahren (einfache Schreibdichte).

Die Aufzeichnungsformate sind frei programmierbar, so dass alle geläufigen Formate lese- und schreibbar sind.

Die Schaltung erlaubt den Anschluss von Laufwerken mit einem und zwei Lese-/Schreibköpfen.

Unterstützt wird im Zeitmultiplexbetrieb die Arbeit von bis zu vier FD-Laufwerken, so dass auch parallele Suchoperationen realisierbar sind.

Der Einsatz der FDCI-Steuereinheit erfolgt in diskettenorientierten Mikrorechnersystemen. Sie ist in ein CP/M-kompatibles Betriebssystem eingebunden.

## 2. Technische Daten

|                                               |                                                                                                                |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Steckleinheitenabmessungen                    | 95 mm x 170 mm                                                                                                 |

| Elektrischer und mechanischer Systemanschluss | K 1520 Systembus nach<br>TGL 37 271                                                                            |

| Steckverbinder                                | 1 x 58-polig, indirekt<br>Bauform 304-58 TGL 29331/03<br>1 x 39-polig, indirekt<br>Bauform 302-39 TGL 29331/04 |

| Systembusanschluss                            | Datenbus (DB00...DB07)<br>Adressbus (AB00...AB07)<br>Steuer signale (/N1, /IORQ,<br>/RD, /WR, /IODI, /RESET)   |

| Stromversorgung                               | + 5 V +/- 5% typ. 800 mA<br>+12 V +/- 5% typ. 40 mA                                                            |

| FDC-Schaltkreis                               | U 8272 D                                                                                                       |

| Quarztyp                                      | HQ 02 16000 kHz<br>TCL 43 380                                                                                  |

| Grundtakt FDC                                 | 4000 kHz fuer 5 1/4-Zoll LW<br>3000 kHz fuer 8-Zoll LW                                                         |

| Floppy Disk Laufwerkstypen                    | 5 1/4" - Laufwerke<br>3" - Laufwerke<br>einfach und Doppelkopflauf-<br>werke (SS, DS)                          |

| Aufzeichnungsverfahren                        | FM- Frequenzmodulations-<br>verfahren<br>MFM- modifiziertes FM-Ver-<br>fahren                                  |

| Laufwerk-Interface                            | Ausgangsstufen Open-Collector                                                                                  |

|                                               | Leitungstreiber 75450 PC<br>7406 PC                                                                            |

|                                               | Leitungsempfaenger DL 014 D                                                                                    |

| Ausgangssignale                               | TTL-Pegel, Low aktiv                                                                                           |

| Adressierung der STE                          | Einstellen der Basisadresse<br>ueber Wickelbruecken<br>XW 0...3                                                |

### 3. Funktionsbeschreibung

Die Steuereinheit stellt das ~~Bindelied~~ zwischen einem Mikrorechner und den Floppy-Disk-Laufwerken dar. Ihre Aufgabe besteht darin, die Daten zwischen dem Speicher des Mikrorechners und dem Laufwerk zu uebertragen und dabei die unterschiedlichen Datenformate aneinander anzupassen. Die Schnittstelle zum Mikrorechner stellt der K 1520-Systembus dar, auf dem die Daten und Adressen parallel uebertragen werden. Die Uebertragungsrate an der Schnittstelle wird im wesentlichen durch die elektr. Eigenschaften des Systembus festgelegt.

Die Baugruppenadresserkennung und Portauswahl erfolgt durch eine Standardschaltung (Komparator/Adressdecoder).

Die Steuersignaldecodierung wird mittels eines PROM, der die Richtungssteuerung des Datenbustreibers, die Generierung des STE-Signals fuer das Laufwerkfunktionsregister und der baugruppeninternen Steuersignale realisiert, durchgefuehrt.

Die Datenleitungen der Baugruppe sind ueber einen Bustreiber mit dem Systembus verbunden.

Parameter, die nicht bei der Initialisierung des Controllers uebertragen, jedoch der Steuerung auf der Baugruppe und der Laufwerke dienen, werden im Laufwerkfunktionsregister gespeichert.

Grundbaustein dieser Baugruppe ist der Controller-Schaltkreis U 8272. Er ermoeglicht den Anschluss von bis zu vier FD-Laufwerken in einem Mikrorechnersystem.

Er stellt entsprechende Signale zur Steuerung der Laufwerke bereit, realisiert die Parallel-/Seriell- bzw. Seriell-/Parallel-Wandlung der Daten, die Adressmarkenerkennung, die CRC-Bytes-Berechnung und Pruefung.

Der Controller fuehrt, nach der Initialisierung (Kommando-/Parameter-Uebergabe) durch den Prozessor, selbstaendig das Kommando aus.

Mit wenigen Befehlen koennen somit komplexe Suchoperationen und vollstaendige Datenuebertragungen ausgeloesst werden.

Der U 8272 liefert Steuersignale, die den Anschluss einer externen PLL (Phase locked loop) und einer Praecompensationschaltung vereinfachen.

Die Praecompensationslogik dient der Vorkompensation der Schreibdaten (nur beim MFM-Aufzeichnungsverfahren), um den "Peak-Shift"-Effekt zu kompensieren.

An der Schnittstelle zum Laufwerk werden die Daten, entsprechend der seriellen Aufzeichnung auf der Magnetplatte, bitseriell uebertragen.

Bei den Leseoperationen sind die von der Magnetplatte ankommenden Daten durch eine PLL-Schaltung zu synchronisieren. Die PLL ermoeglicht Datenleseoperationen von FM- und MFM-codierten Daten. Die Generierung des Datenfensters DW ermoeglicht dem Controller, entsprechend der Polaritaet des Datenfensters, die Trennung der Synchronisations- und Datenimpulse vorzunehmen.

Die Peripherieankopplung erfolgt ueber Leitungstreiber und -empfaenger.

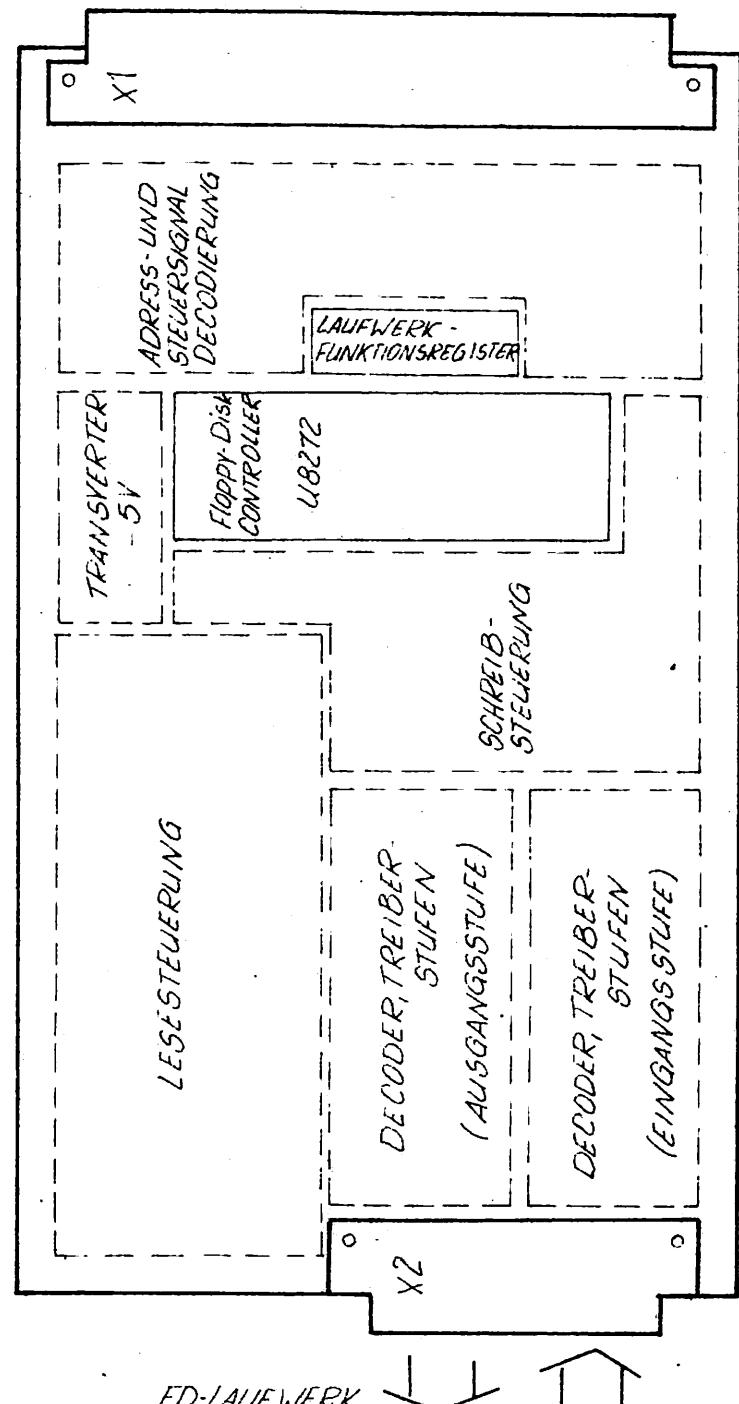

### 3.1 Funktionsgruppen

Die FDCI-Steuereinheit besteht im wesentlichen aus folgenden Funktionsgruppen (siehe Funktionsplan Fp(1)):

- Busankopplung, Adress- und Steuersignaldecodierung

- FD-Controller und Laufwerkfunktionsregister

- Schreibsteuerung

- Takterzeugung

- Schreibtaktgenerierung WRCLK

- Praecompensation

- Lesesteuerung

- Datenseparator/PLL

- Peripherieankopplung

- Leitungsempfaenger und Leitungstreiber

- Transverter

#### 3.1.1 Busankopplung

##### 3.1.1.1 Adress- und Steuersignaldecodierung

Der K 1520-Systembus stellt die Schnittstelle zwischen der ZRE und der FDCI-Steuereinheit dar.

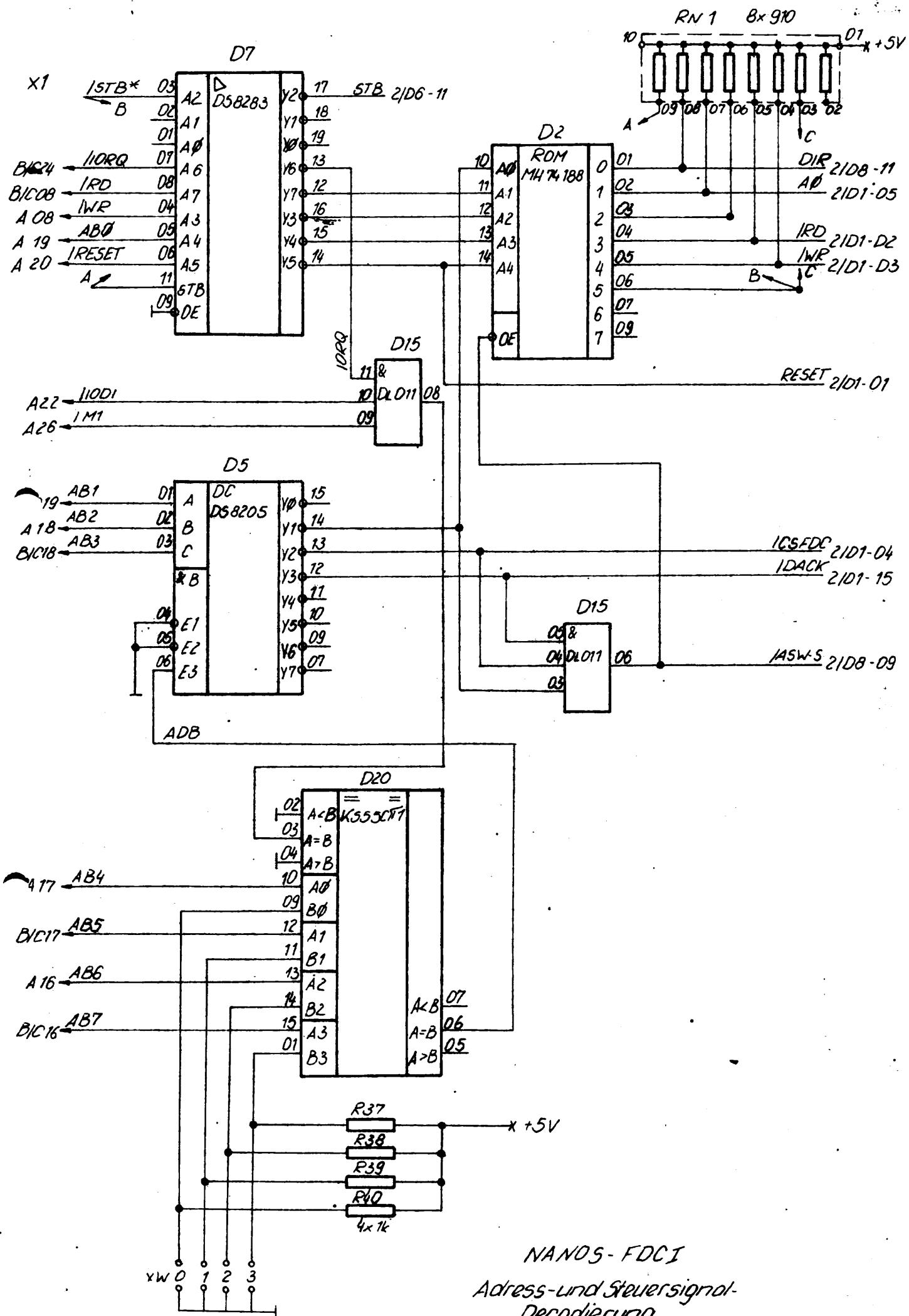

Die Systembussignale sind dem Steckverbinder X1 zugordnet. Bild 1 Sp(3) zeigt die detaillierte Darstellung der Steuer- signal- und Adressdecodierung.

Die Auswahl der Baugruppe erfolgt durch die Auswertung der Bussteuersignale /M1, /IORQ, /IODI und der Adressleitungen AB04...AB07 mittels des Komparators D20 (K555 CM1).

Das Baugruppen-Selectsignal ADB (high-aktiv) wird durch folgende Bedingung beschrieben:

$$ADB = /M1 \cdot /IORQ \cdot /IODI \cdot (AB04 \cdot AB05 \cdot AB06 \cdot AB07)$$

Das Signal /IODI ermöglicht, die Baugruppe auch bei gültiger Adresse abzuschalten.

Bei gültiger Baugruppenadresse wird durch das Signal ADB der Adressdecoder D5 (DS 8205) aktiviert. Dieser realisiert die Auswahl der Bausteine in Abhängigkeit von den Adress- signalen AB01..AB03 (siehe Tabelle).

| Adressbits |      |      | Auswahlsignal | Baustein     |

|------------|------|------|---------------|--------------|

| AB03       | AB02 | AB01 |               |              |

| 0          | 0    | 0    | n. b.         |              |

| 0          | 0    | 1    | /STB*         | LWFkt.Reg.*) |

| 0          | 1    | 0    | /CS           | FDC          |

| 0          | 1    | 1    | /DACK         | FDC          |

| 1          | 0    | 0    | n. b.         |              |

| 1          | 0    | 1    | n. b.         |              |

| 1          | 1    | 0    | n. b.         |              |

| 1          | 1    | 1    | n. b.         |              |

\*) Bemerkung: Das Signal STB wird durch die log. Verknuepfung der Signale /STB\* und /VR (Systemsignal) gebildet. Mit Aktivierung des Signal STB werden die Daten vom internen Datenbus auf den Ausgang des Laufwerkfunktionsregister geschalten und mit der H/L-Flanke gespeichert.

Gleichzeitig werden der Datenbustreiber D8 (DS 2236) und der PROM D2 (I<sub>H</sub> 74168) durch das Signal /ASW-S aktiviert.

Durch die Verknuepfung der Ausgangssignale des Decoders D5 ueber das AND-Gatter D15.2 (log.ODER), erfolgt die Generierung des Selectsignals /ASW-S (low-aktiv).

Die Baustein-Selectsignale werden durch die Auswertung des Adreszssignals AB 00 spezifiziert.

Steuerung der Baugruppe erfolgt ueber 6 Portadresen mit den Funktionen:

rel. Adresse

|      |                                                            |

|------|------------------------------------------------------------|

| 02 H | "Laden Laufwerksfunktionsregister"                         |

| 03 H | n. b.                                                      |

| 04 H | "Lesen Hauptstatusregister des FDC-Bausteins"              |

| 05 H | "Lesen bzw. Schreiben der Datenregister des FDC-Bausteins" |

| 06 H | "DACK-Freigabe fuer DMA-Betrieb" *)                        |

| 07 H |                                                            |

\*) Bemerkung: Das Signal /DACK wird generiert, um in Verbindung mit dem Signal /DRQ bei der Erweiterung der Schaltung mit einem DMA-Schaltkreis einen direkten Speicherzugriff zu ermoeglichen.

Zur Minimierung des Hardwareaufwandes der Steuersignaldecodierung wurde ein PROM eingesetzt.

Der PROM D2 realisiert die Richtungssteuerung des Datenbusstrebers D8, die Generierung des Signals STB (s.o. Bemerkung) und der baugruppeninternen Steuersignale A0, /RD und /WR (siehe Pkt. 3.1.3).

Über den Datenbusstreiber D8 sind die Datenein- und -ausgaenge der Baugruppe mit dem Datenbus des Rechners verbunden. Die Datenrichtungsumschaltung erfolgt durch das Signal DIR. D8 ist im Grundzustand inaktiv. Die Steuerlogik (PROM D2) zur Bildung des Signals DIR ist so konzipiert, dass die Eingaenge des Treibers zum Systembus gerichtet sind. Der DIR-Eingang (Pin 11) führt H-Potential. Eine Richtungsumschaltung (DIR L-Pegel) erfolgt nur bei aktivem Baugruppen-Selectsignal ADB und /RD-Signal.

### 3.1.1.2 Baugruppenadressierung

Die Baugruppenadresse wird durch die Leitbrücke XW0...3 an den B-Eingaengen von D20 eingestellt.

Die Zuordnung der Adressbits zu den Leitbrücken ist folgende:

| Leitbrücken | Adressbits  |

|-------------|-------------|

| XW 0        | ..... AB 04 |

| XW 1        | ..... AB 05 |

| XW 2        | ..... AB 06 |

| XW 3        | ..... AB 07 |

Eine offene Brücke verlangt für die entsprechende Adressleitung H-Potential, während für eine geschlossene Brücke demzufolge L-Potential gefordert wird.

Im NANOS-Mikrorechnersystem ist für die FDCI-Steuereinheit die Vorzugsadresse 90H festgelegt.

92H Steu port

94H Komandoport

95H Date port

### 3.1.2 Laufwerkfunktionsregister

Das Laufwerkfunktionsregister D9 (DS 8262) wird über die Portadresse 92H angesprochen. Es werden Parameter, die der Steuerung auf der Baugruppe, sowie der Ansteuerung der Antriebsmotoren der FD-Laufwerke dienen, gespeichert.

Mit der H/L-Flanke des STB-Signals erfolgt die Übernahme der Parameter vom Datenbus in das Register.

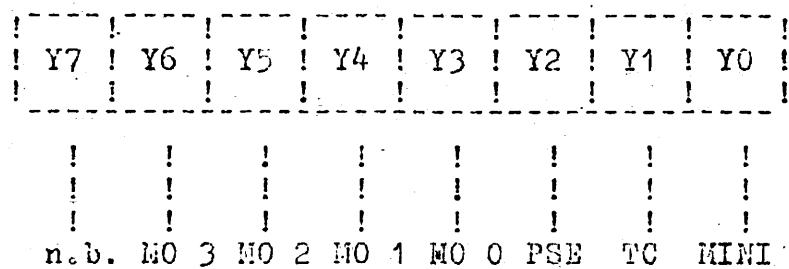

In Abbildung 1 wird die Bedeutung der Bits dargestellt. Das Bit Y0 (Signal MINI) wird bei Verwendung von MINI-Laufwerken (5 1/4-Zoll) gesetzt. Das Signal MINI (H-Pegel) bewirkt, dass der Basistakt C von 8000 kHz auf 4000 kHz herabgesetzt wird.

Bit Y1 (Signal TC) bildet das Abbruchsignal fuer den Controller.

Das Bit Y2 (Praecompensation-Selectsignal PSE) erlaubt das Abschalten der vom Controller U 8272 beim HFM-Aufzeichnungsverfahren staendig generierten Preshift-Signale PS0,1 und damit der Vorcompensation der Schreibdaten.

Das Einschalten des Signals PSE bewirkt eine staendige Vorcompensation der Schreibdaten (siehe Pkt.3.1.4.3).

Mit den Bits Y3...Y6 (M0 0...3) kann man die Antriebsmotoren der entsprechenden FD-Laufwerke schalten. In der Regel wird der Motor nur eingeschaltet, wenn ein Zugriff auf das Laufwerk erfolgen soll.

Bild 1 : Bedeutung der Bits im Laufwerkfunktionsregister

Bit Y0      Signal MINI - Umschaltung der Taktfrequenz

Pegel H: Minilaufwerk      C = 4000 kHz

L: Standardlaufwerk      C = 8000 kHz

Bit Y1      Signal TC - Beendigung eines Kommandos

Pegel H: Abbruchsignal fuer FDC

L: inaktiv

Bit Y2      Signal PSE - Praecompensation-Selectsignal

Pegel H: Praecompensation der Schreibdaten

L: Praecompensation abgeschalten

Bits Y3...6 Signale M0 0...M0 3 - Einschaltsignale fuer FD-Laufwerk antriebsmotoren

Pegel H: Motor einschalten,

Verriegelung ein

L: Motor ausschalten,

Verriegelung aus

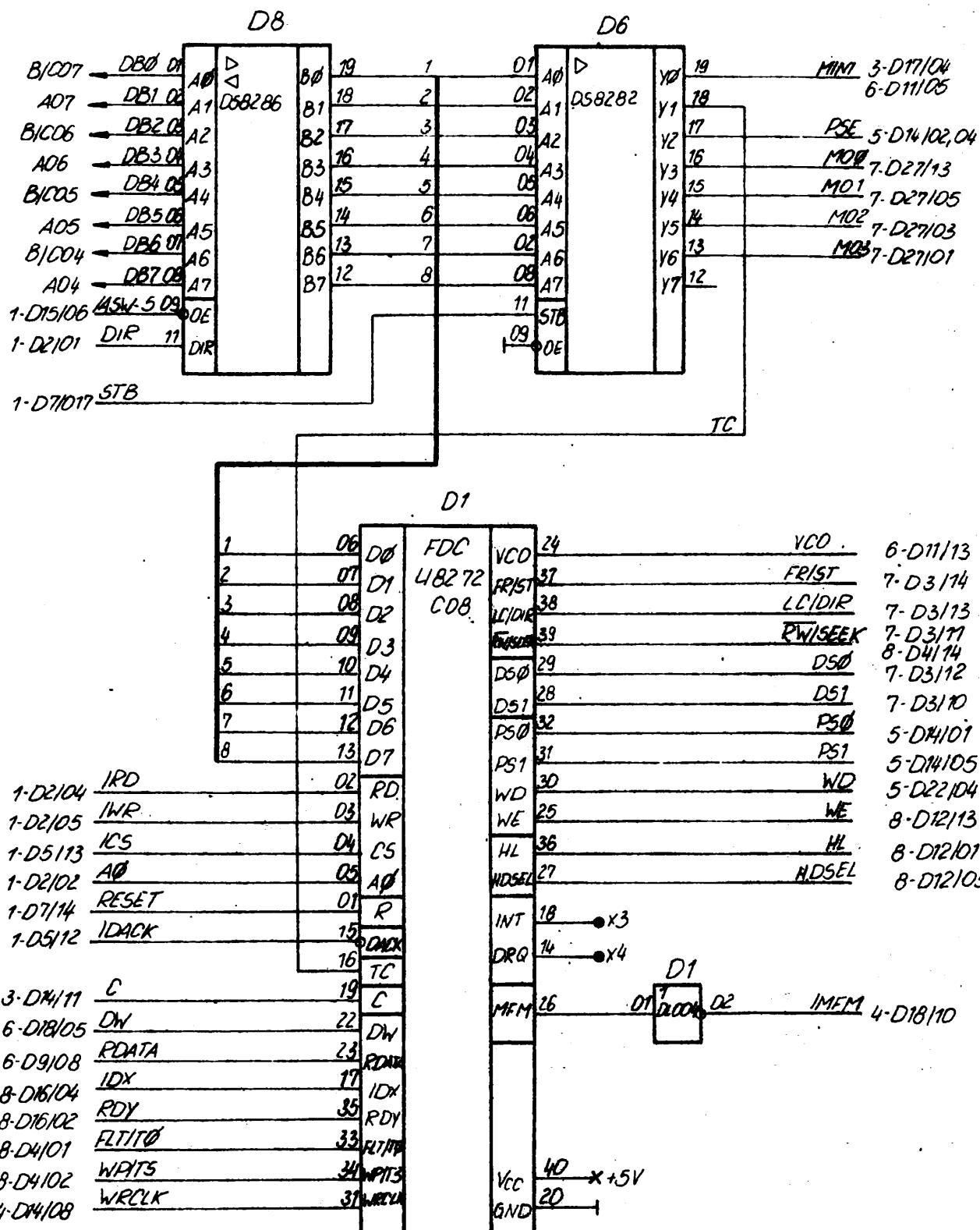

### 3.1.3 Floppy-Disk Controller

Der Controller-Schaltkreis U 8272 ist der Grundbaustein der FDCI-Anschlusseinheit. Er steuert die Ablaeufe in den FD-Laufwerken und deren Datenverkehr mit dem Mikrorechner. Wie in Plt. 3 bereits beschrieben, werden durch den Controller wesentliche Funktionen, wie die Parallel-/Seriell- bzw. Seriell-/Parallel-Umsetzung der Daten, die CRC-Bytes Berechnung und Ueberpruefung, die Adressmarkenerkennung, sowie die Bereitstellung der Steuersignale fuer den Anschluss von bis zu vier FD-Laufwerken realisiert.

Es koennen Standard und Minilaufwerke mit einem bzw. zwei Schreib/Lesekoepfen angesteuert werden.

Er liefert Steuersignale, die den Anschluss einer externen PLL, die der Synchronisation der Lesedaten vom FD-Laufwerk dient, und einer Praecompenationschaltung vereinfacht. Die Aufzeichnung der Daten erfolgt mit dem FM- bzw. MFM-Aufzeichnungsverfahren.

Die Adressierung erfolgt ueber die Portadressen 94H und 95H. Der Prozessor kann auf zwei Register des FDC, ein Hauptstatus- und ein Datenregister, zugreifen.

Das 8-Bit Hauptstatusregister, das die Statusinformationen des Controllers enthaelt, kann vom Prozessor zu beliebigen Zeiten abgefragt werden. Es wird ueber die Portadresse 94H angesprochen.

Definition der Bits des Hauptstatusregisters:

| Bit  | Symbol | Beschreibung                                                                                                                      |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| DB 0 | DOB    | FD-LW 0 aktiv                                                                                                                     |

| DB 1 | D1B    | FD-LW 1 aktiv                                                                                                                     |

| DB 2 | D2B    | FD-LW 2 aktiv                                                                                                                     |

| DB 3 | D3B    | FD-LW 3 aktiv                                                                                                                     |

| DB 4 | CD     | Les- bzw. Schreibkommando in Bearbeitung                                                                                          |

| DB 5 | NDM    | FDC im Nicht-DMA-Betrieb (nur waehrend Ausfuehrungsphase gesetzt, Uebergang nach L-Potential zeigt Ende der Ausfuehrungsphase an) |

| DB 6 | DI0    | Richtung der Datenuebertragung<br>H-Potential - zum Prozessor<br>L-Potential - zum Datenreg.                                      |

| DB 7 | RQM    | Bereitschaftsmeldung des FDC                                                                                                      |

Das 8-Bit Datenregister besteht aus mehreren Registern (Stapelregister), wobei immer nur ein Register zu einer bestimmten Zeit mit dem Datenbus verbunden ist. Es werden Daten, Kommandos, Parameter und Laufwerkstatusinformationen

gespeichert. Dieses Register kann ueber die Portadresse 95H ausgelesen bzw. eingeschrieben werden.

Der Zusammenhang zwischen den baugruppeninternen Signalen A0, /RD und /WR und den o.g. Registern zeigt folgende Tabelle.

| A0 | /RD | /WR | Funktion                    |

|----|-----|-----|-----------------------------|

| L  | L   | H   | Lesen Hauptstatusregister   |

| L  | H   | L   | verboten                    |

| L  | L   | L   | verboten                    |

| H  | L   | L   | verboten                    |

| H  | L   | H   | Lesen vom Datenregister     |

| H  | H   | L   | Schreiben ins Datenregister |

|    |     |     |                             |

Die Steuersignaldecodierung ueber den PROM D2 erfolgt gemaess der Schaltkreisspezifikation, so dass die verbotenen Funktionen nicht auftreten koennen.

Der FDC kann im DMA- oder im Nicht-DMA-Betrieb arbeiten. Die Konfiguration der Steuereinheit unterstuetzt den Nicht-DMA-Betrieb, ist jedoch fuer eine Erweiterung der Schaltung offen gestaltet (siehe Anmerkungen Pkt. 3.1.1.1). Der Datentransfer zwischen dem Prozessor und dem Controller erfolgt im Polling-Mode.

Mit nur 15 Befehlen laesst sich der Controller-Schaltkreis programmieren; per Software kann auch die Schrittgeschwindigkeit des Schrittmotors usw. sowie die Sektoraenge (128, 256, 512, 1024 Byte) eingestellt werden. Der U 8272 D kann 15 separate Kommandos ausfuehren.

#### Die Befehlsliste des Controllers

- Lese Daten

- Lese geschuetzte Daten

- Lese eine Spur

- Lese ID-Marke

- Durchsuchen auf Gleichheit

- Durchsuchen auf kleiner oder gleich

- Durchsuchen auf groesser oder gleich

- Schreibe Daten

- Schreibe geschuetzte Daten

- Formatiere eine Spur

- Positionieren auf Spur 0

- Pruefen Interruptstatus

- Spezifizieren (Uebergabe Laufwerksparameter)

- Abfrage Laufwerkstatus

- Suchen (Positionieren auf Spur XX)

Man unterscheidet bei den Kommandos 3 Phasen:

- Kommandophase der Controller erhaelt alle fuer eine Operation notwendigen Informationen vom Prozessor.

- Ausfuehrungsphase Ausfuehrung des Kommandos

- Resultatsphase nach dem Abschluss der Operation werden Status- und andere Informationen fur den Prozessor bereitgestellt

Während der Kommando- oder Resultatsphase muss das Hauptstatusregister durch den Prozessor gelesen werden, bevor jedes Informationsbyte ins bzw. vom Datenregister geschrieben oder gelesen wird. Eine Byteübertragung darf nur erfolgen, wenn das Hauptstatusregister die Bereitschaft des FDC meldet. Die Bits 6 und 7 (D10, RQH) ermöglichen es, den Datenverkehr entsprechend zu realisieren.

Das Lesen des Hauptstatusregisters in der Ausfuehrungsphase ist nur im Nicht-DMA-Betrieb erforderlich. Die Datenuebertragung im READ-DATA-MODE (Lese-Daten-Betrieb) bzw. WRITE-DATA-MODE (Schreib-Daten-Betrieb) zwischen dem Prozessor und dem Controller ist, gemaecc den durch die Schaltkreispezifikation vorgegebenen Zeitbedingungen, zu realisieren (nur in der Ausfuehrungsphase relevant). Insbesondere beim Aufzeichnungsverfahren KFI ist die Uebertragung der Datenbytes zeitkritisch.

Die entsprechenden Angaben sind der Technischen Beschreibung des FDC U 3272 D zu entnehmen.

Die Ausführungsphase wird durch das vom Prozessor gesendete Abbruchsignal TC beendet.

Das Kommando wird nur richtig beendet, wenn in der Resultatsphase die entsprechenden Bytes gelesen wurden. Die Statusregister 0..3 koennen nur in der Resultatsphase gelesen werden.

Jedes vom Prozessor an die FDCI-Steuereinheit gegebene Kommando erfordert eine Mehrfach-Byteübertragung. Dabei werden Informationen, wie die Adresse des anzusteuernenden Laufwerks, Aufzeichnungsverfahren (SD/DD), Laufwerkstyp, Definition des Datenformats u.a. in den Parameterbytes des Datenregisters abgespeichert. Es löst einen dafür charakteristischen Funktionsablauf aus.

Mach Beendigung des Kommandos kann die Uebertragung des Resultates (Statusinformationen usw.) zum Prozessor ebenfalls eine Mehrfach-Byteuebertragung sein. Diese Daten müssen in allgemeinen der Prozessor vom FDC abfragen.

Mit den entsprechenden Befehlen kann man komplexe Suchoperationen und vollstaendige Datenuebertragungen auslösen, die vom Controller selbstständig ausgeführt werden.

Die Aufzeichnungsformate sind frei programmierbar. Die ID-Felder, die Adressfelder der einzelnen Sektoren einer Spur, koennen frei waehlbare Werte annehmen, da es sich um logische Parameter handelt.

Der eigentliche Datentransfer zwischen dem Controller und dem Prozessor erfolgt mit den Befehlen "Lese Daten" bzw. "Schreibe Daten".

Soll z.B. ein Sektor auf einer Floppy-Disk gelesen werden, so ueberprueft der Controller die Spurnummer, Sektornummer und deren CRC-Pruefbytes, bevor er das anschliessende Datenfeld zum Prozessor uebertraegt.

Die Initialisierung einer Diskette erfolgt mit dem Kommando FORMAT A TRACK. Die verschiedenen GAPS (Luecken), PADS (Umschaltfelder) und ID-Felder koennen beliebig konfiguriert werden (siehe Pkt. 4.5 Programm FORMAT).

Die Initialisierung des Controllers erfolgt durch das Kommando "SPECIFY", dabei werden die Parameter Schritt- ratenzeit, Kopfladezeit und Kopfentladzeit zum FDC ueber- tragen und die internen Zaehler ~~einstellt~~.

Die Laufwerkselect-Signale DS 0/1 werden kurzzeitig aktiviert und damit automatisch die Laufwerke auf ihren Bereitschaftstatus (Signal /RDY) hin ueberprueft.

Da der FDC-Schaltkreis staendig den Status der Laufwerke abfragt, ist es erforderlich das Ready-Signal unabhaengig vom Signal /HL (Kopfladen) zu generieren (siehe Anmerkungen Pkt. 5).

Die Beschreibung des Controllers U 8272 D kann, wegen der hohen Komplexitaet dieses Schaltkreises, nur informativen Charakter tragen. Entsprechende Informationen sind der Technischen Beschreibung des U 8272 D zu entnehmen.

### 3.1.4 Schreibsteuerung

Die Schreibsteuerung besteht im wesentlichen aus dem quarzstabilisierten Taktgenerator, der Schaltung fuer die Schreibtaktgenerierung WRCLK und der Praecompenstationsschaltung.

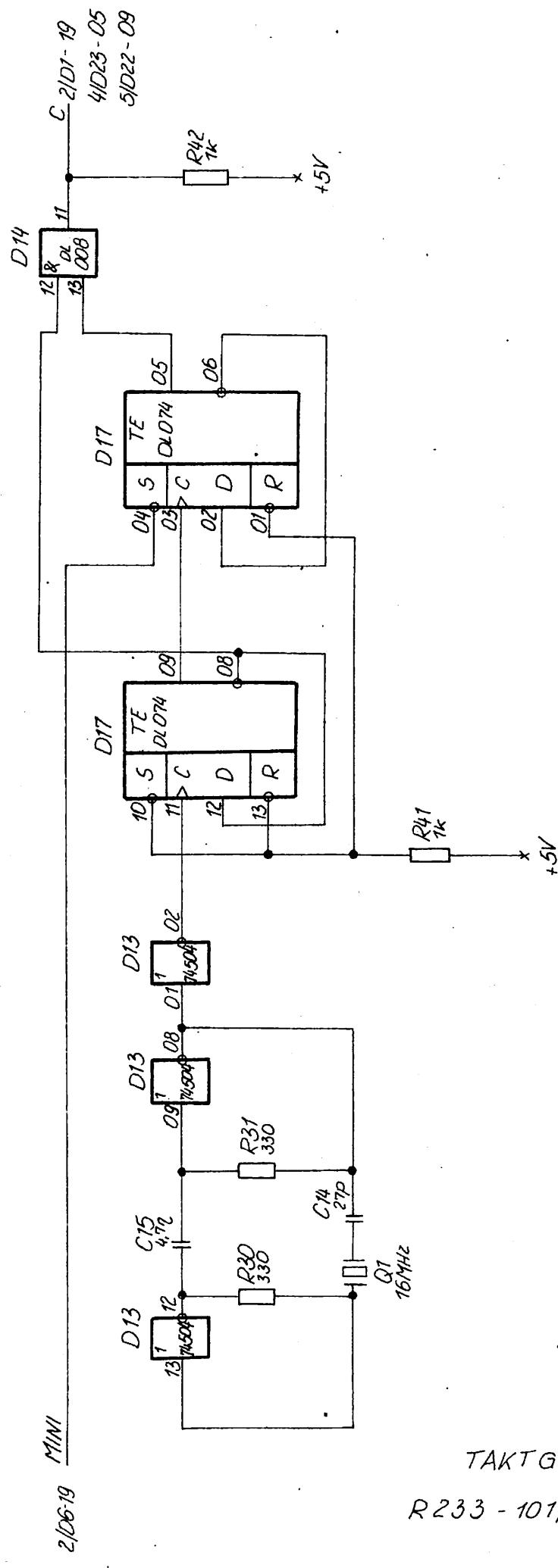

#### 3.1.4.1 Takterzeugung

Der quarzstabile Oszillatator mit den Invertern D13.4 und D13.6 (MH 74 S04) erzeugt mit dem Quarz Q1 eine Grundfrequenz von 16000 kHz. Der nachfolgende Inverter D13.1 dient der Impulsformung, sowie der Entkopplung der nachfolgenden Schaltung vom Taktgenerator.

Von der Taktfrequenz wird der Basistakt C fuer den FD-Controller und die Generierung des Schreibtaktes WRCLK abgeleitet.

In Abhaengigkeit vom Steuersignal MINI (siehe Pkt. 3.1.2) erfolgt durch die D-FF's D17.2 und D17.1 (DL 074) eine Teilung der Grundfrequenz auf 8000 bzw. 4000 kHz.

| Laufwerkstyp | Signal MINI | Basisfrequenz |

|--------------|-------------|---------------|

| 5 1/4 -Zoll  | H-Potential | 4000 kHz      |

| 8 -Zoll      | L-Potential | 8000 kHz      |

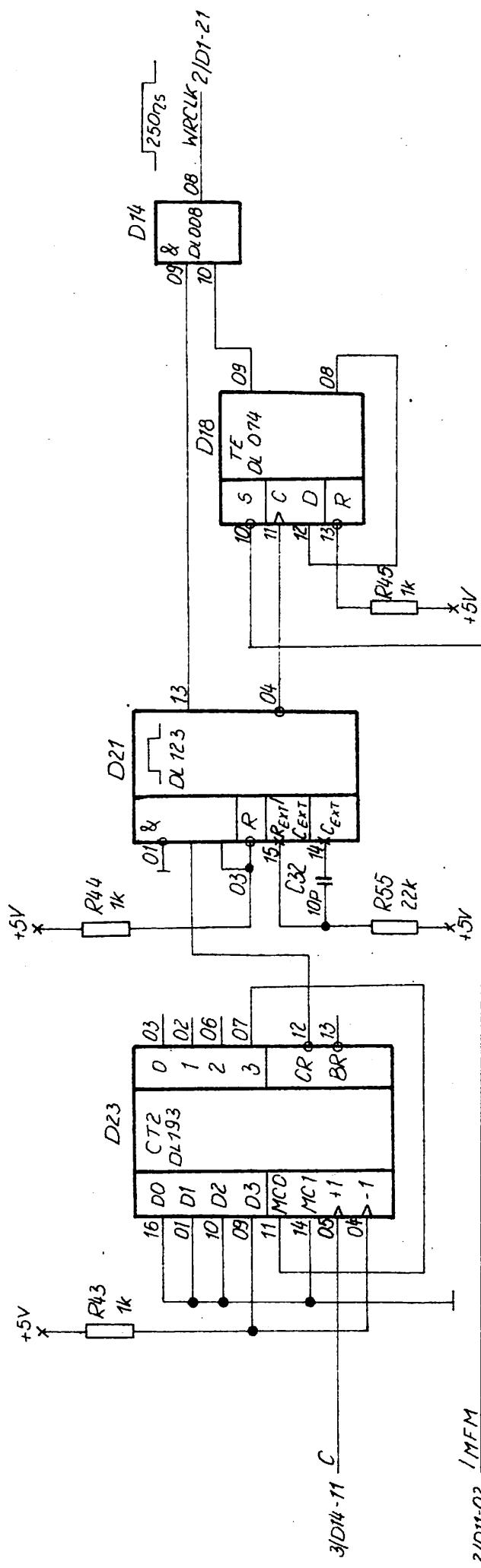

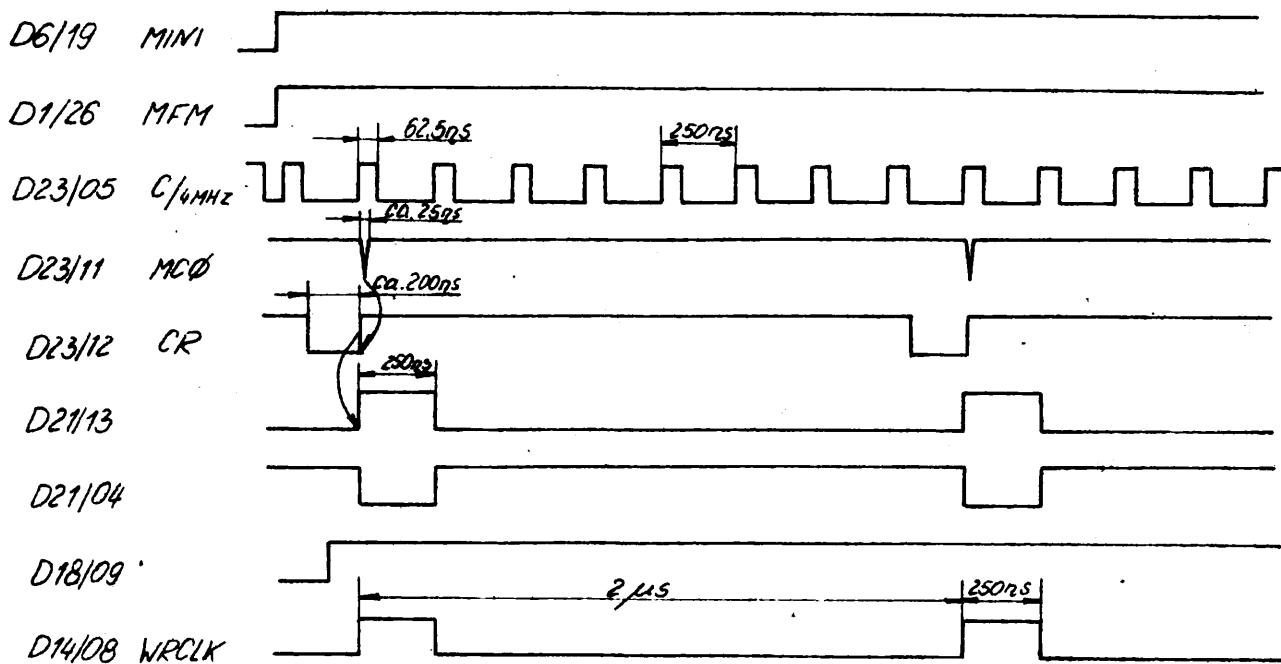

#### 3.1.4.2 Schreibtaktgenerierung WRCLK

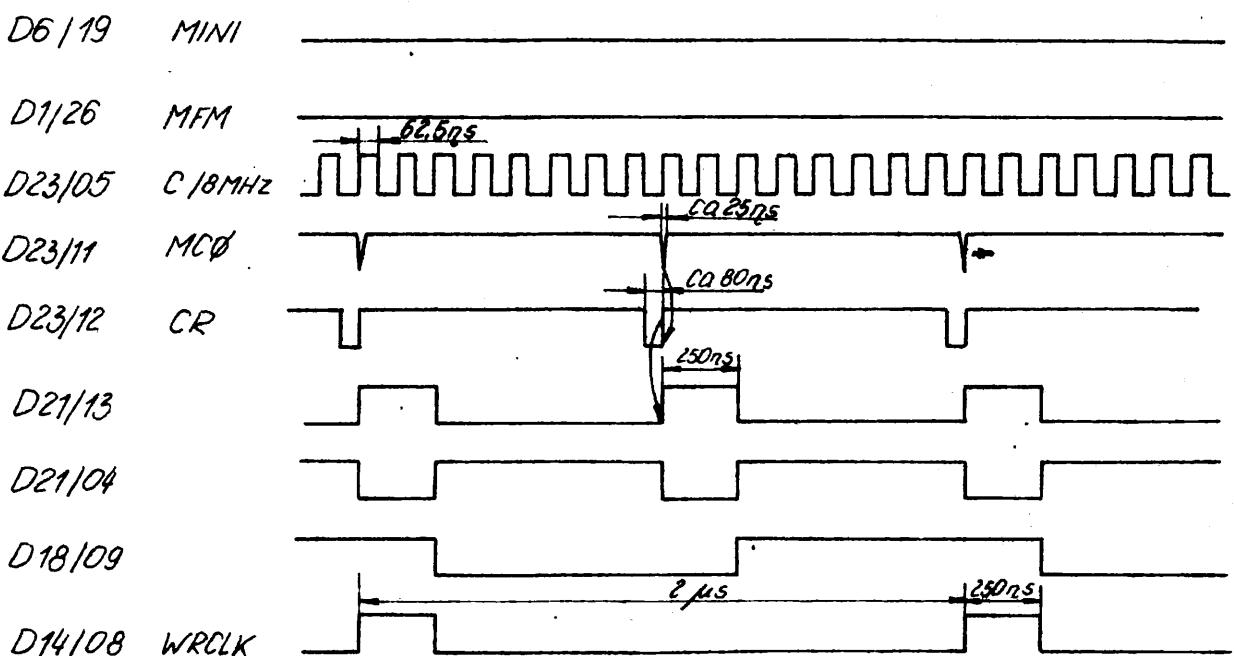

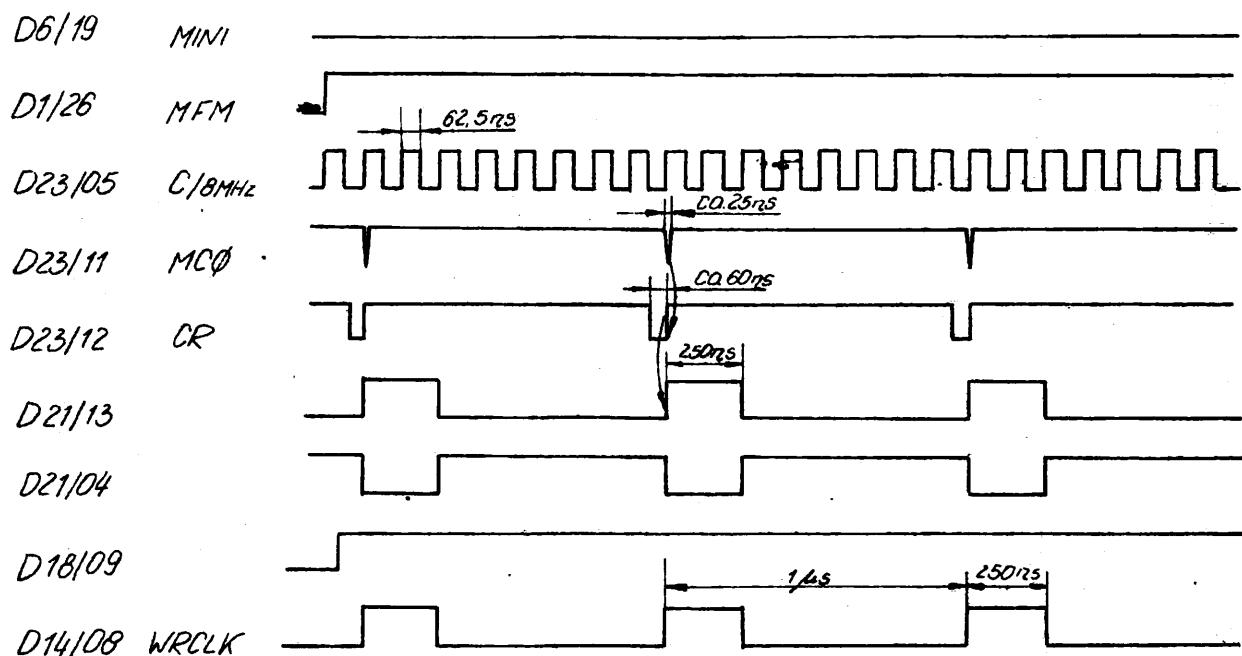

Der Basistakt C wird ueber den Frequenzteiler D23 (DL 193) mit dem Faktor 8 heruntergeteilt. Anschliessend wird durch das Monoflop D21.1 (DL 123) die H-Impulsbreite des Schreibtaktes WRCLK auf 250 ns festgelegt (Schaltkreisspezifikation).

Beim Aufzeichnungsverfahren FM erfolgt eine Frequenzteilung dieses Signals durch das D-FF D18.2 (DL 074).

Ueber das AND-Gatter D14.3 (DL 008) wird der Schreibtakt WRCLK an den Controller gefuehrt.

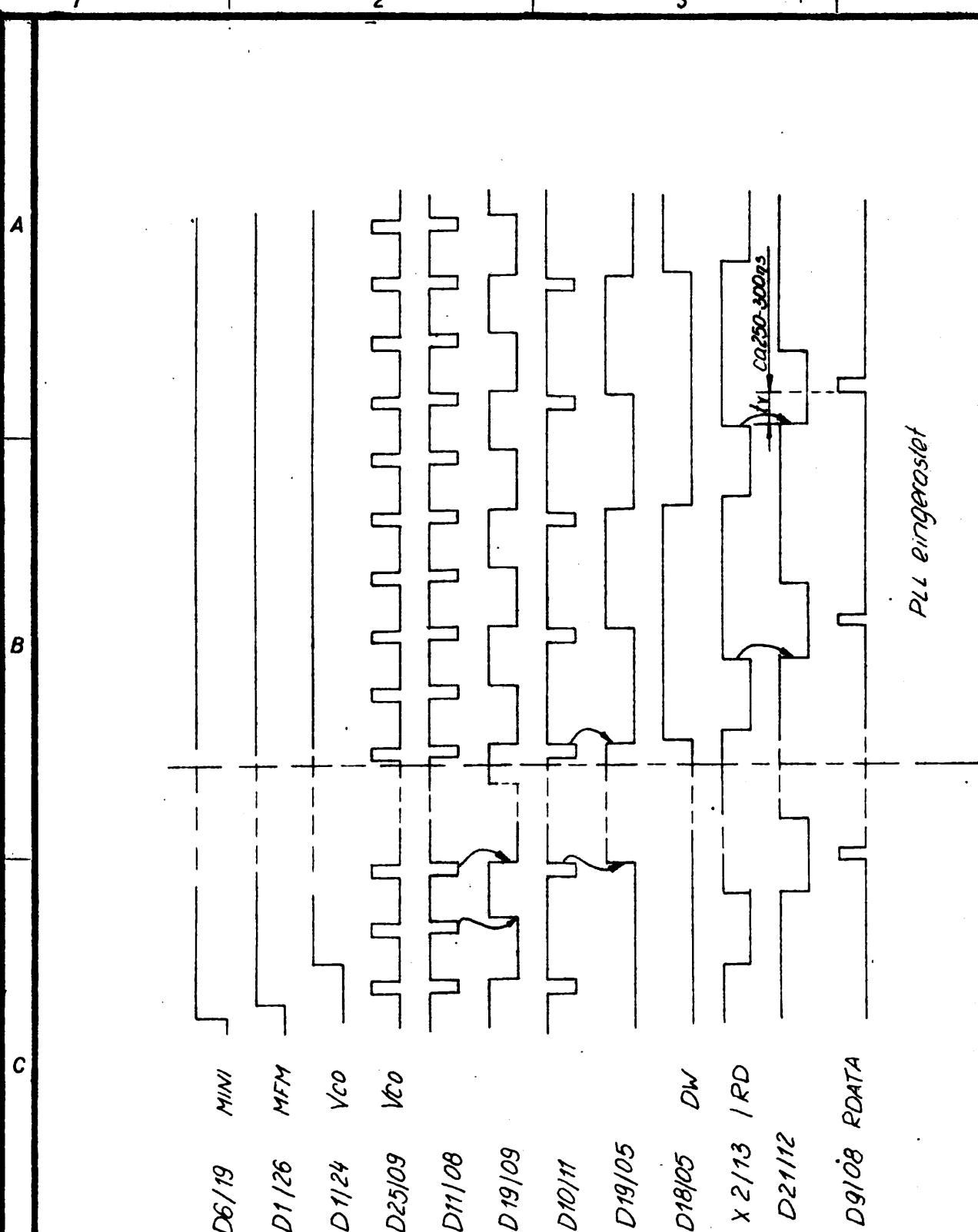

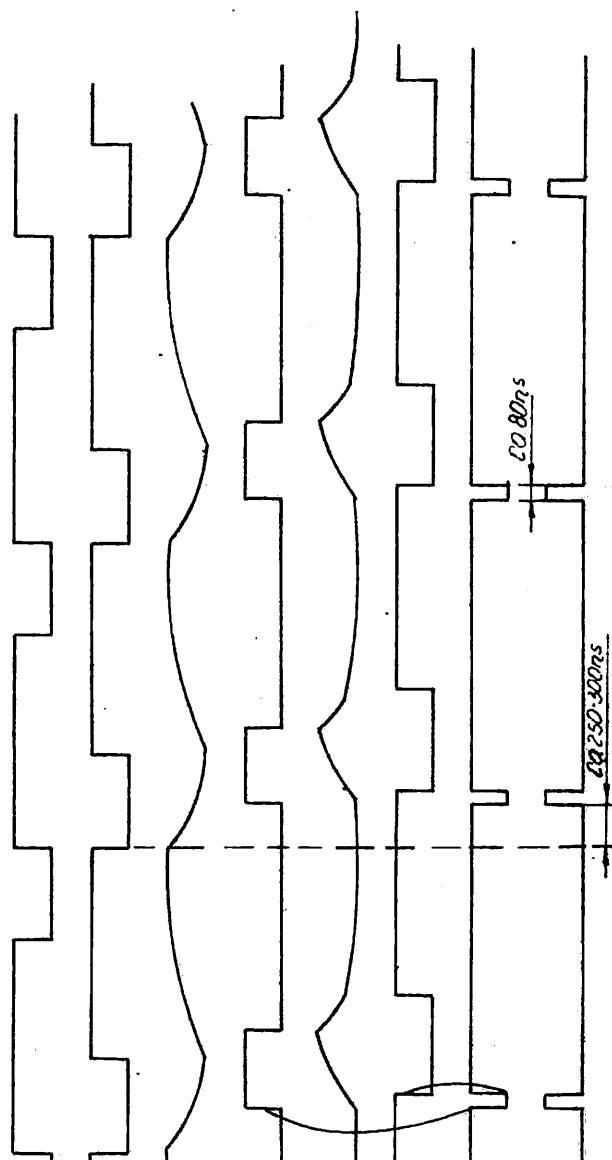

In den Impulsdiaagrammen Abb. 2...4 ( siehe Anhang) werden die zeitl. Ablaeufe dargestellt.

| Laufwerkstyp | Aufzeichnungsverfahren | Schreibtakt          |

|--------------|------------------------|----------------------|

| 5 1/4-Zoll   | MFM                    | 500 kHz (2 $\mu$ s)  |

| 8 -Zoll      | FM                     | 500 kHz (2 $\mu$ s)  |

| 8 -Zoll      | HFM                    | 1000 kHz (1 $\mu$ s) |

Der Schreibtakt wird intern im Controllerschaltkreis mit den zu schreibenden Daten verknüpft. Dieses serielle Takt-Daten-Gemisch liegt als Schreibsignal (FH- bzw. MFM-Impulsfolge) am Controllerausgang WRDATA an.

### 3.1.4.3 Praecompensation der Schreibdaten

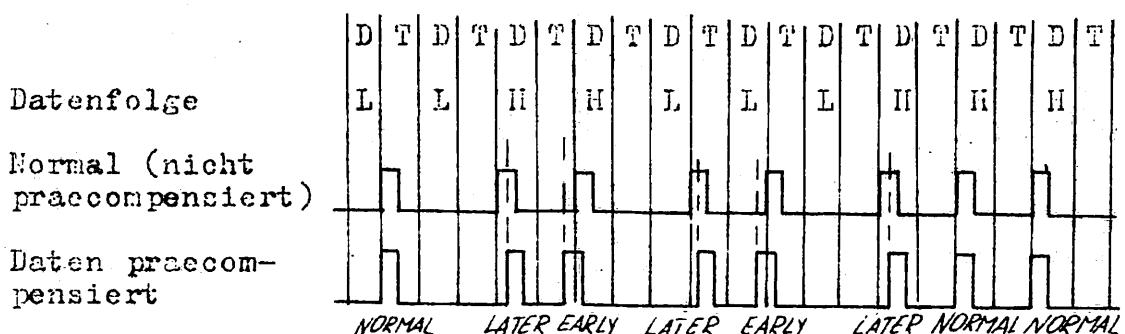

Beim Lesen der Daten, die mit erhöhter Aufzeichnungsdichte auf der Magnetplatte aufgezeichnet wurden, tritt der Effekt des magnet. Spitzenversatzes ("Peak-Shift"-Effekt) auf. Er erschwert die Synchronisation der PLL (Phase locked loop) und führt zu Datenfehlern.

Demzufolge ist bereits beim Schreiben der Daten eine Vorkompensation durchzuführen.

Diese Korrekturmöglichkeit ergibt sich aus der Tatsache, dass der "Peak-Shift"-Effekt nach einem bestimmten Algorithmus vorhersagbar ist (siehe Bild 5). Er tritt an den Übergängen von max. Bitdichte auf groessere Bitabstände und umgekehrt auf.

Die Praecompensation ist dabei nur bei doppelter Aufzeichnungsdichte (Aufzeichnungsverfahren MFM) relevant.

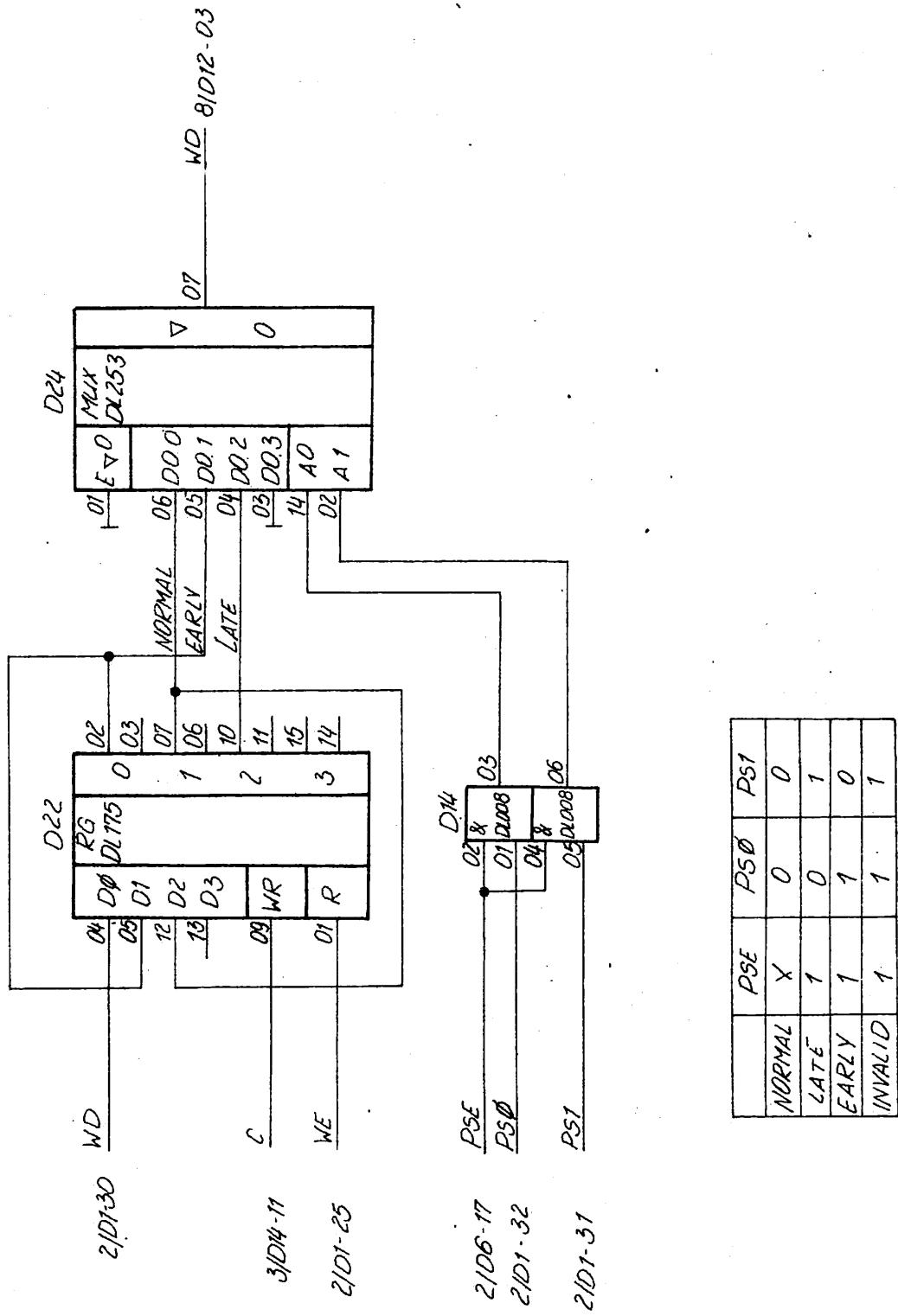

Bild 5 : Praecompensation einer Impulsfolge

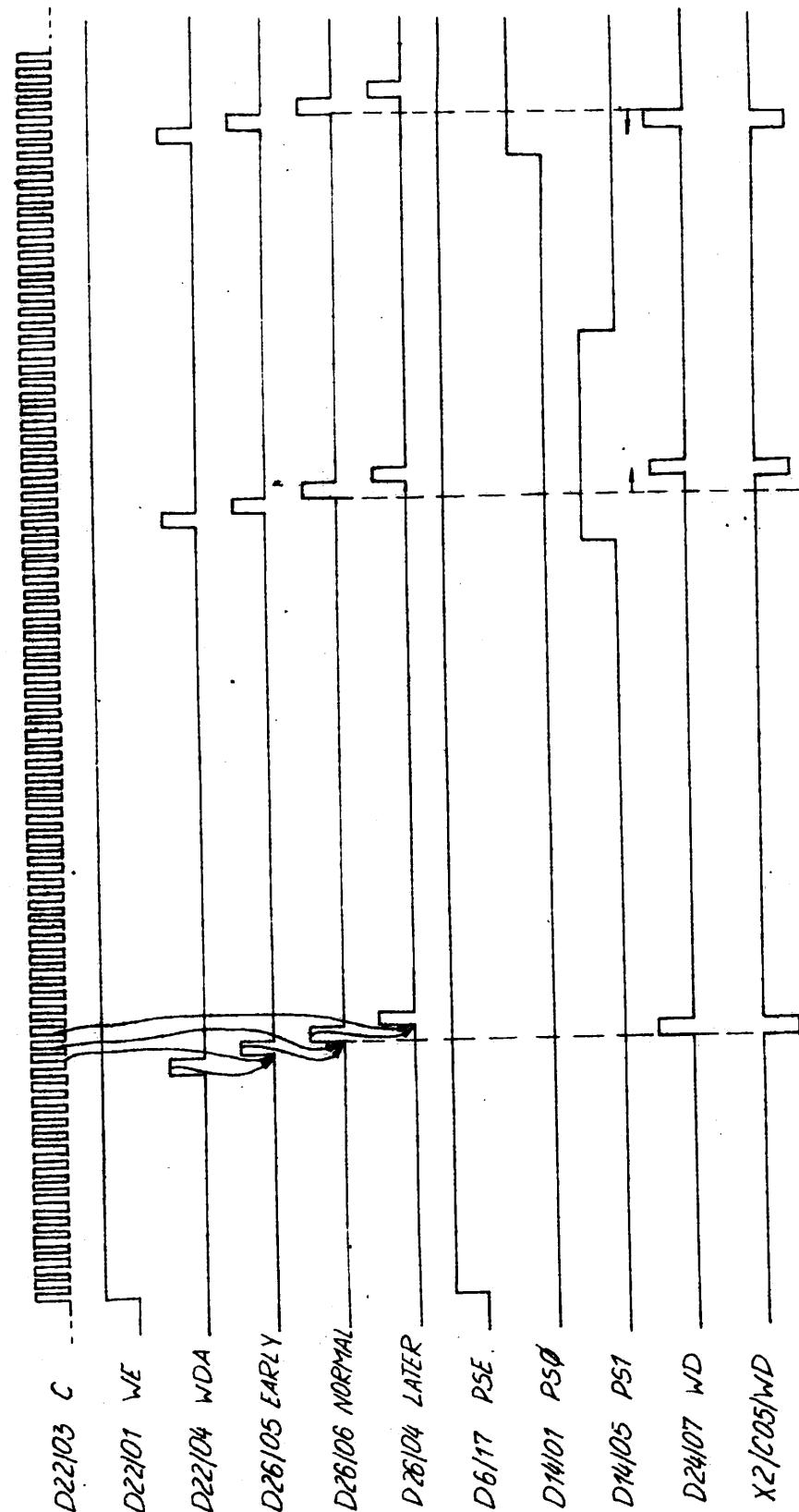

Die Schaltung wird im Stromlaufplan Sp(1) Bl.7, die zeitlichen Abläufe im Impulsdigramm Abb. 6 (siehe Anhang) dargestellt.

Die Schreibdaten WRDATA werden mit dem Takt C in das Register D22 (DL 175) geschoben und liegen um die entsprechenden Taktperioden verzögert an den Eingängen des Multiplexers D24 (DL 253) an.

Gleichzeitig werden die Preshift-Signale PS0 und PS1 bei aktivem Praecompensations-Selectsignal PSE über die AND-Gatter D14.1 und D14.2 (DL 003) an die Steuereingänge von D24 durchgeschalten.

Die vom Controller-Schaltkreis generierten Ausgangssignale PS0 und PS1 ermöglichen eine vom Laufwerkhersteller vorgeschriebene Verschiebung des Schreibsignals. Diese zeitliche Verschiebung, die als Praecompensationszeit definiert ist, wird in der realisierten Schaltung durch die Taktfrequenz C

bestimmt. Die Praecompensationszeit zeigt an, um wieviel die Bits der Schreibdaten frueher, spaeter oder normal aufgezeichnet werden.

Praecompensationszeit: 125 ns bei Standard-LW (8")

250 ns bei MINI-LW (5 1/4")

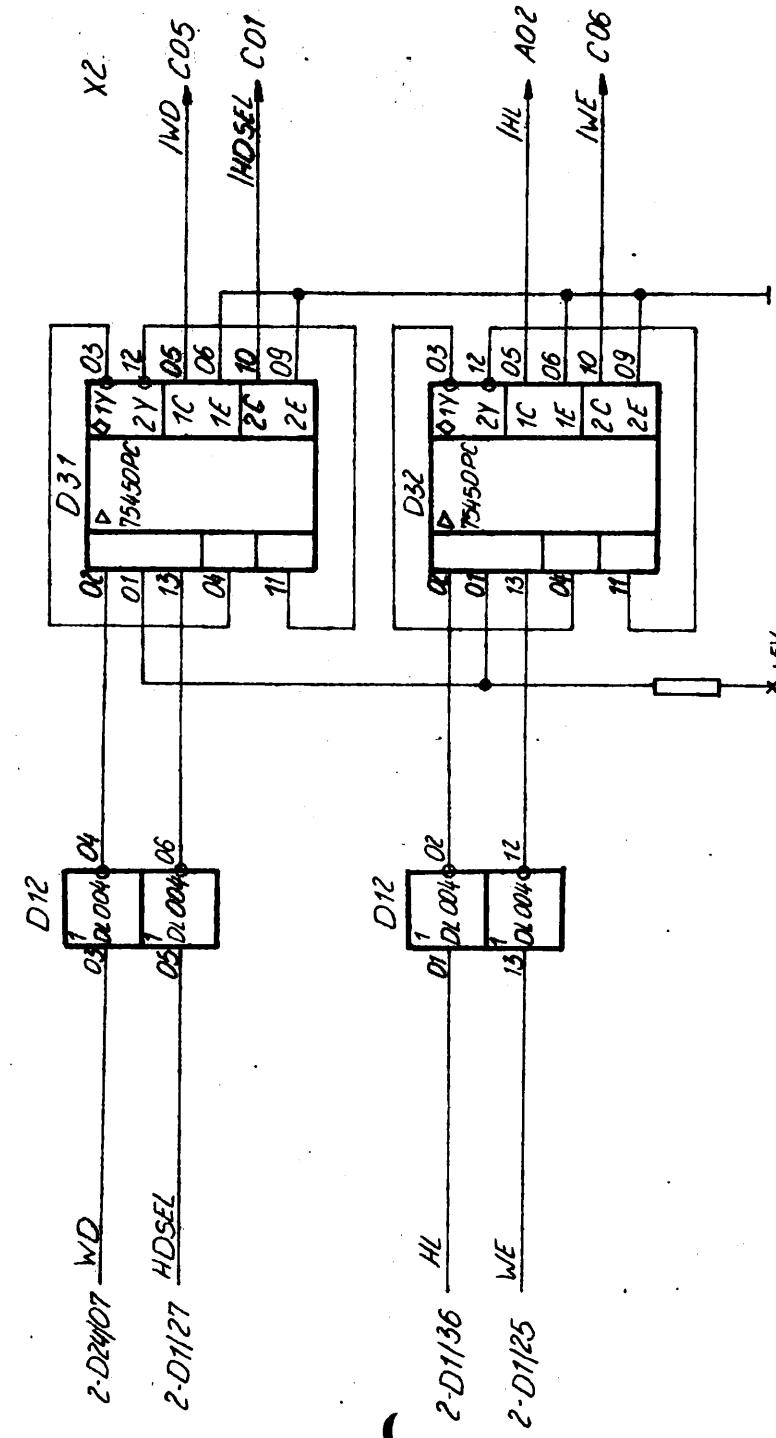

Das Schreibsignal WD wird durch den Inverter D12.1 negiert, den Leitungstreiber D31.1 (75450 PC) verstaeckt und zum Steckvorbinder X2 gefuehrt.

Der o.g. Effekt tritt auf Grund der hoheren Aufzeichnungsdichte in den inneren Spuren der Magnetplatte auf, so dass die Praecompensation der Schreibdaten nur in diesem Bereich erfolgt.

Das Selectsignal PSE wird softwaremaessig im Laufwerkfunktionsregister D6 eingeschalten.

Aus den technischen Beschreibungen der Floppy-Disk-Laufwerke sind entsprechende Hinweise darueber zu entnehmen, ab welcher Spur die Praecompensation der Schreibdaten durchzufuehren ist.

### 3.1.5 Lesesteuerung-Datenseparator

Die Lesesteuerung hat folgende Funktionen zu erfüllen:

- Synchronisation der Lesedaten (/RD)

- Generierung Datenfenster DW

- Impulsverkuerzung und -verzoegerung Lesesignal

Sie beinhaltet die fuer die Lesooperationen notwendige PLL-Schaltung, die Datenlesooperationen von MFM- und FM-codierten Daten ermoeglicht.

Die PLL hat die Aufgabe die ankommenen Daten (/RD-Signal) zu sychronisieren, um Fchlerquellen, die weitestgehend durch mechanische Toleranzen der Laufwerke, Drehzahlabweichungen des Antriebssystems und der magnet.Eigenschaften der Magnetplatte gegeben sind, zu kompensieren.

Die Gencrierung des Datenfenster DW dient zum Abtasten der Lesedaten, d.h. der Controller fuehrt entsprechend der Polariitaet von DW eine Trennung zwischen den Synchronisations- und den eigentlichen Datenimpulsen durch. Das Datenfenster DW wird als der Bereich definiert, in dem ein Datenbit sicher und zuverlaessig erkannt werden kann.

Die Impulsverkuerzung und -verzoegerung des /RD-Signals ermoeglicht eine genaue Auswertung der Daten im Controller.

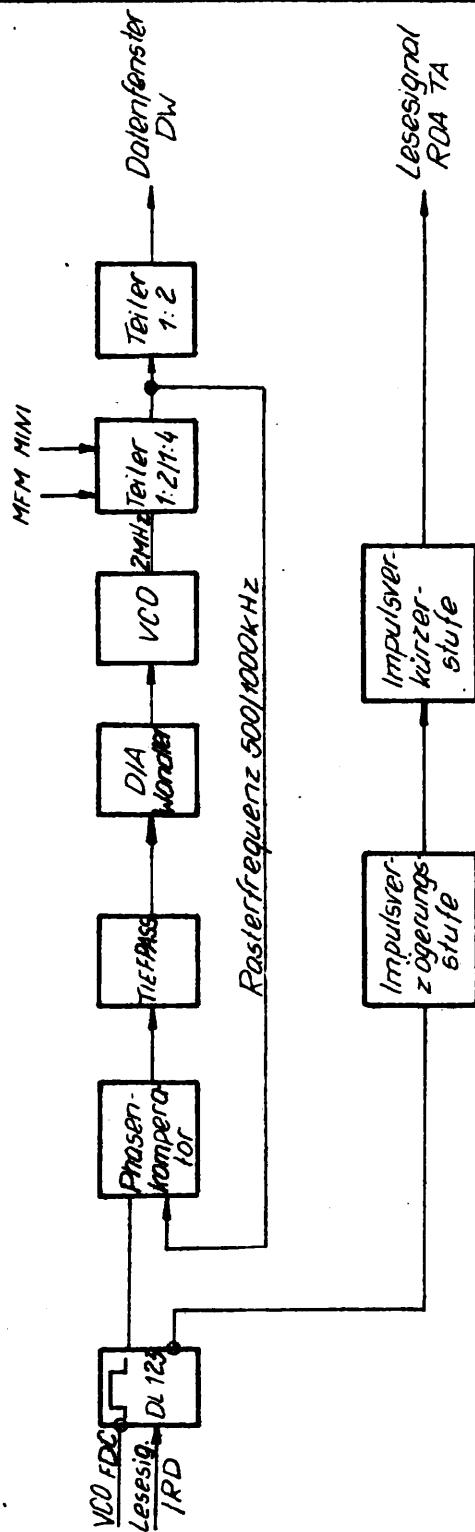

Im Blockschaltbild der Lesesteuerung Abb. 7 (siehe Anhang) sind die Funktionsbloecke des Datenseparators dargestellt.

### 3.1.5.1 Wirkungsweise der PLL

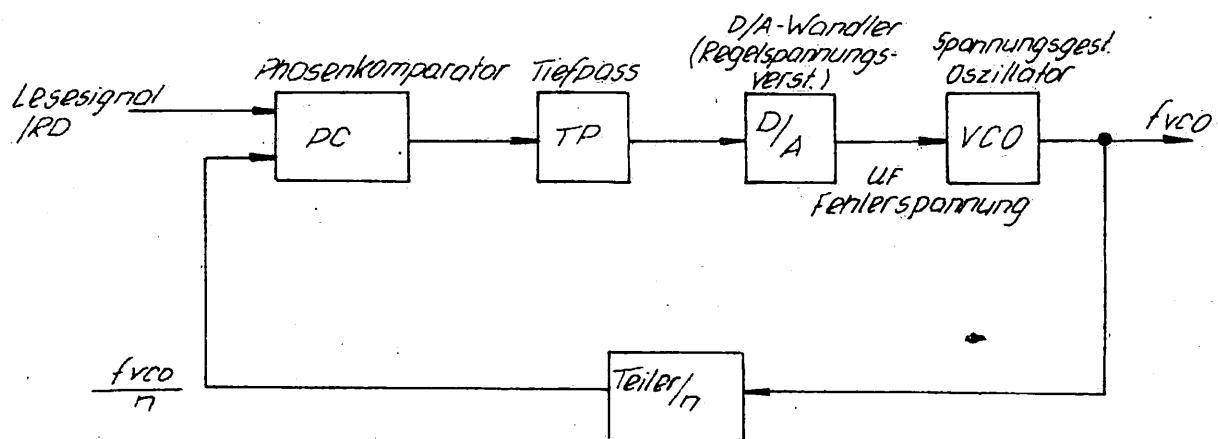

Die PLL ist ein Regelsystem, das es gestattet, die Frequenz und Phasenlage eines spannungsgesteuerten Oszillators (VCO) mit der Frequenz und Phase eines Eingangssignals zu synchronisieren, d.h. in ein festes definiertes Verhältnis zu bringen.

Die PLL besteht aus der Phasenvergleichsschaltung (Phasenkomparator), dem Tiefpassfilter (Lag-Lead-Filter), dem Regelspannungsverstärker, dem spannungsgesteuerten Oszillator (VCO) und einem schaltbaren Teiler.

Das Blockschaltbild der PLL ist in Abb. 8 dargestellt.

Abb. 8 : Blockschaltbild PLL

Der Synchronisationsvorgang beginnt mit dem Anlegen des Eingangssignal /RD an den Phasenkomparator. Dieser vergleicht Frequenz und Phase des Eingangssignals mit der geteilten VCO-Frequenz (Rasterfrequenz) und ermittelt daraus eine Fehlerspannung. Der Tiefpass wandelt das digitale Fehlersignal in eine Gleichspannungsdifferenz um, die durch den Operationsverstärker verstärkt und auf den Steuereingang des VCO geführt wird. Diese regelt dessen Ausgangsfrequenz so lange nach, bis die Frequenz des Eingangssignals und die der geteilten VCO-Frequenz übereinstimmen. Die PLL ist damit "eingerastet".

Die VCO-Frequenz wird so geregelt, dass zwischen dem Leseignal /RD und der Rasterfrequenz ein minimaler Phasenfehler und demzufolge eine Fehlerspannung bestehen bleibt. Das bewirkt eine stetige Nachregelung der VCO, so dass die PLL Schwankungen des Eingangssignals folgen kann und dabei eingrastet bleibt.

Fang- und Haltebereich sind wesentliche Kenngrößen, die die Stabilität einer PLL-Schaltung beschreiben.

- Mit Fangbereich werden die Eckfrequenzen ober- und unterhalb der Grundfrequenz der VCO bezeichnet, bei denen die VCO von der Eingangsfrequenz synchronisiert wird.

- Der Haltebereich gibt den Frequenzbereich an, in dem die VCO dem Eingangssignal zu folgen vermag.

### 3.1.5.2 Schaltungsbeschreibung

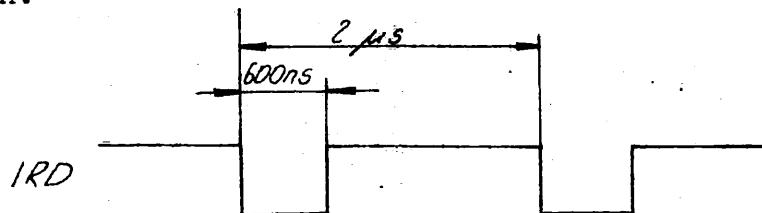

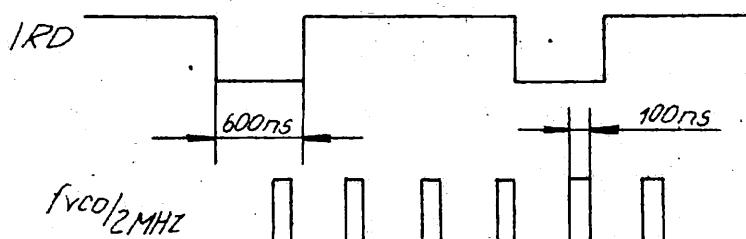

Das Lesesignal /RD (Laufwerkssignal) gelangt an den Eingang des Monoflop D21.2 (DL 123). Mit der L/H-Flanke des /RD-Signals wird D21.2 getriggert.

Es hat die Aufgabe, das Lesesignal zu negieren und eine definierte Impulsbreite von 650 ns zu erzeugen.

Der Ausgang des Monoflop ist auf den Eingang des Phasenkomparators, der aus den NAND-Gattern D10.1 und D10.2 (DL 000) besteht, geführt.

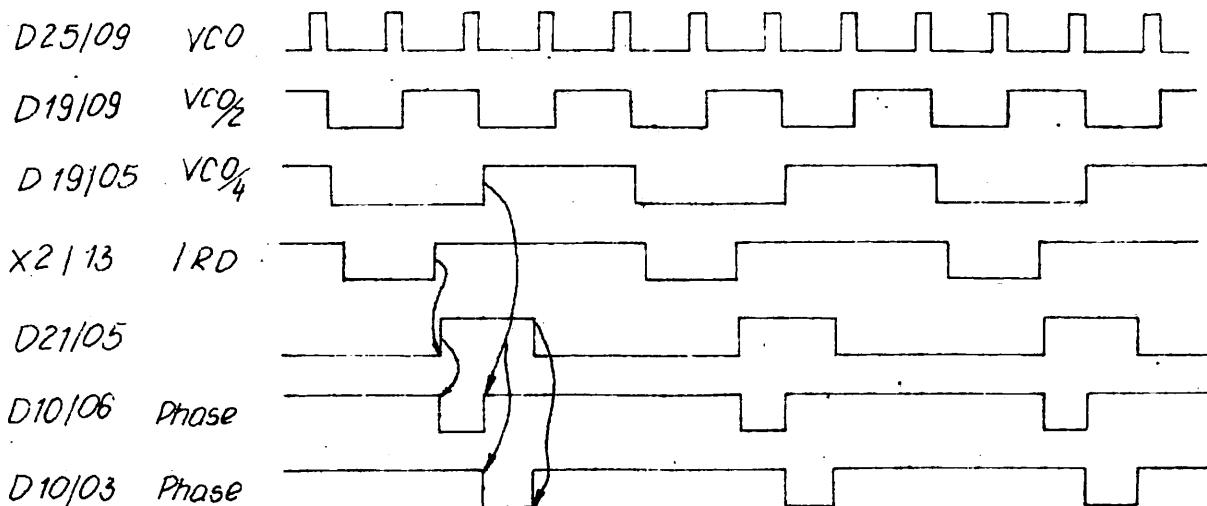

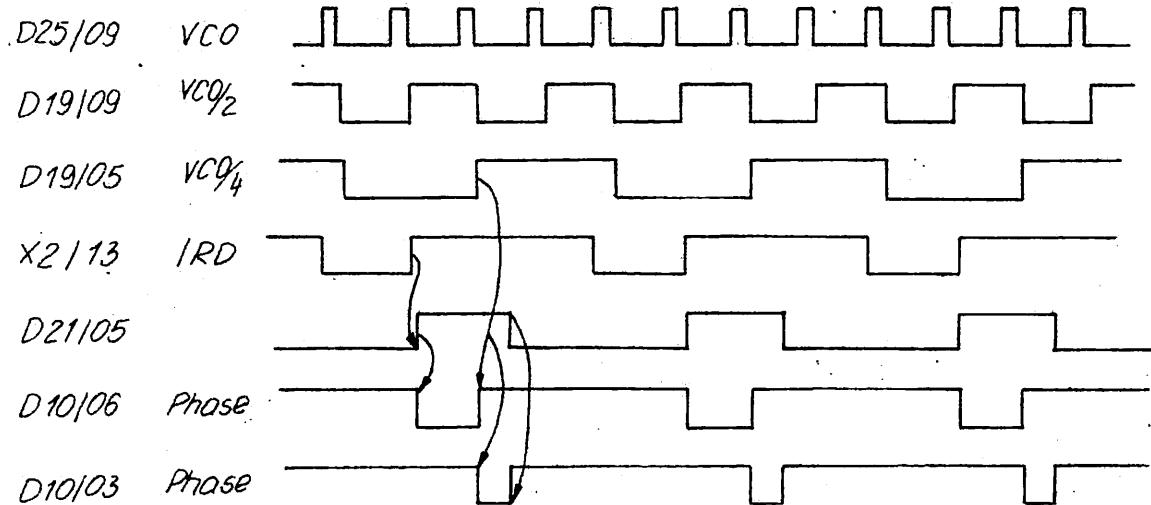

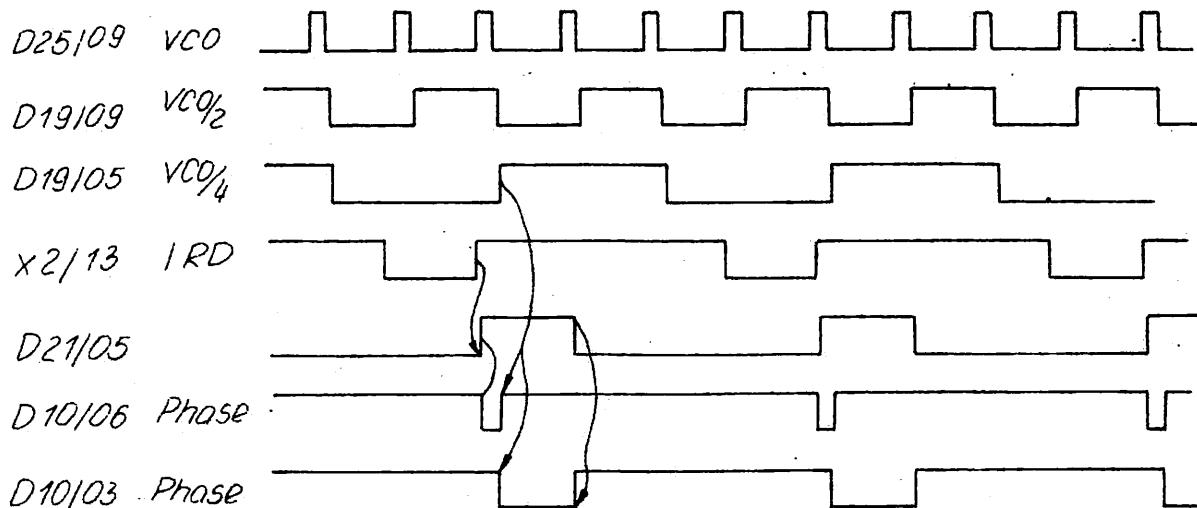

Dieser vergleicht die Eingangsdaten (/RD-Signal) mit dem durch die D-FF's D19.1 und D19.2 (DL 074) geteilten VCO-Takt.

Die Ausgänge des Phasenkomparators gehen auf zwei symmetrisch aufgebaute Tiefpassfilter, die durch R7, R51, C8 und R8, R52, C9 gebildet werden.

Die Filterausgänge liegen an den invertierenden bzw. nicht-invertierenden Eingängen des Operationsverstärkers D26 (WAA 741).

Die Verstärkung des Operationsverstärkers wird durch die Widerstände R57 und R58 bestimmt. Sie sind so dimensioniert, dass ein maximaler Regelbereich des VCO erreicht wird.

Die Dimensionierung der Konstantstromquelle (VT1, R10, R21, C10) und die Schaltschwelle des Komparators D25 (75107 PC) bestimmen die Grundfrequenz des VCO (2 MHz).

Der Arbeitspunkt des Transistors VT1 wird durch R22 und VD5 eingestellt. Über die Emitter-Kollektor-Strecke fließt ein konstanter Strom, der den Kondensator C10 auflädt. Wird die Schwellspannung des Komparators erreicht, erscheint am Ausgang H-Pegel. Dadurch werden die Gatter D27.2 und D27.3 (7406 PC) umgeschaltet und der Kondensator C10 über den Widerstand R3 gegen Masse entladen. Gleichzeitig wird der Spannungsteiler R34, R36, durch die Parallelschaltung des Widerstandes R5 zu R34, verändert und somit die Referenzspannung des Komparators herabgesetzt. Unterschreitet die Spannung über C10 den Wert der Referenzspannung, schaltet der Ausgang von D25 auf L-Pegel. Der Vorgang kann mit dem Aufladen des Kondensators C10 neu beginnen.

Eine Frequenzänderung des /RD-Signals bewirkt eine Veränderung der Fehlerspannung und demzufolge der Basisspannung des Transistors VT1. Dies ruft wiederum eine Veränderung des Ladestroms von C1 und damit der VCO-Frequenz hervor.

In den Impulsdiagrammen Abb. 9...11 (siehe Anhang) werden die zeitliche Ablaeufe des Datenseparators, sowie der PLL-Schaltung bei unterschiedlichen Eingangsfrequenzen dargestellt.

Im synchronisierten Zustand der PLL stehen die Taktimpulse der Rasterfrequenz zu den Datenimpulsen der Eingangsfrequenz in einem festen definierten Verhaeltnis.

Die Generierung des Datenfensters DW erfolgt ueber das D-FF D13.1 (DL 074), durch Teilung der Rasterfrequenz.

Der Controller kann nun entsprechend der Polaritaet des Datenfensters eine Trennung zwischen Synchronisations- und Datenimpulsen vornehmen.

Um eine fehlerfreie Auswertung der Lesedaten durch den Controller-Schaltkreis U 8272 zu gewaehrleisten, werden in einer Sonderbaustufe diese Impulse verzögert und verkuerzt. Die /RD-Impulse werden vom negierten Ausgang des Monoflop D21.2 abgegriffen und ueber eine Verzoegerungs- und Impulsverkuerzerstufe ( R9,C13,D9.4 / R6,C12,D9.1/2 ) an den Eingang des NAND-Gatter D9.3 (DL 000) gefuehrt und anschliessend negiert. Die Impulsbreite des Lesesignals RDATA betraegt ca.80 ns (siehe Impulsdiagramm Abb. 12).

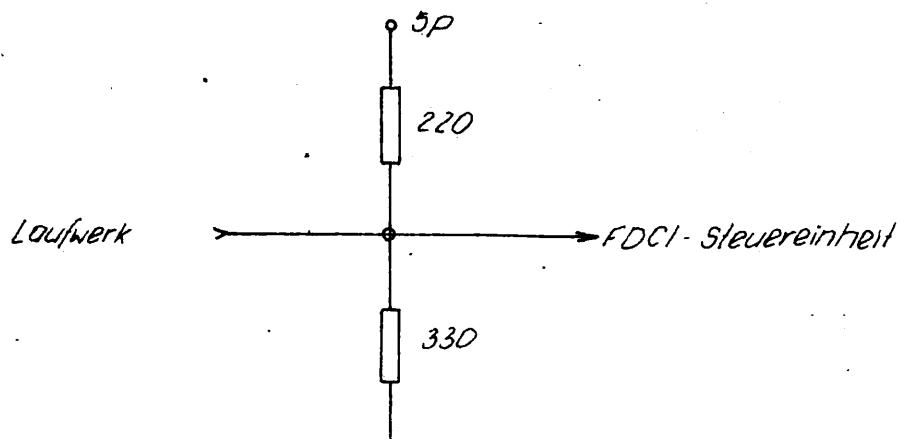

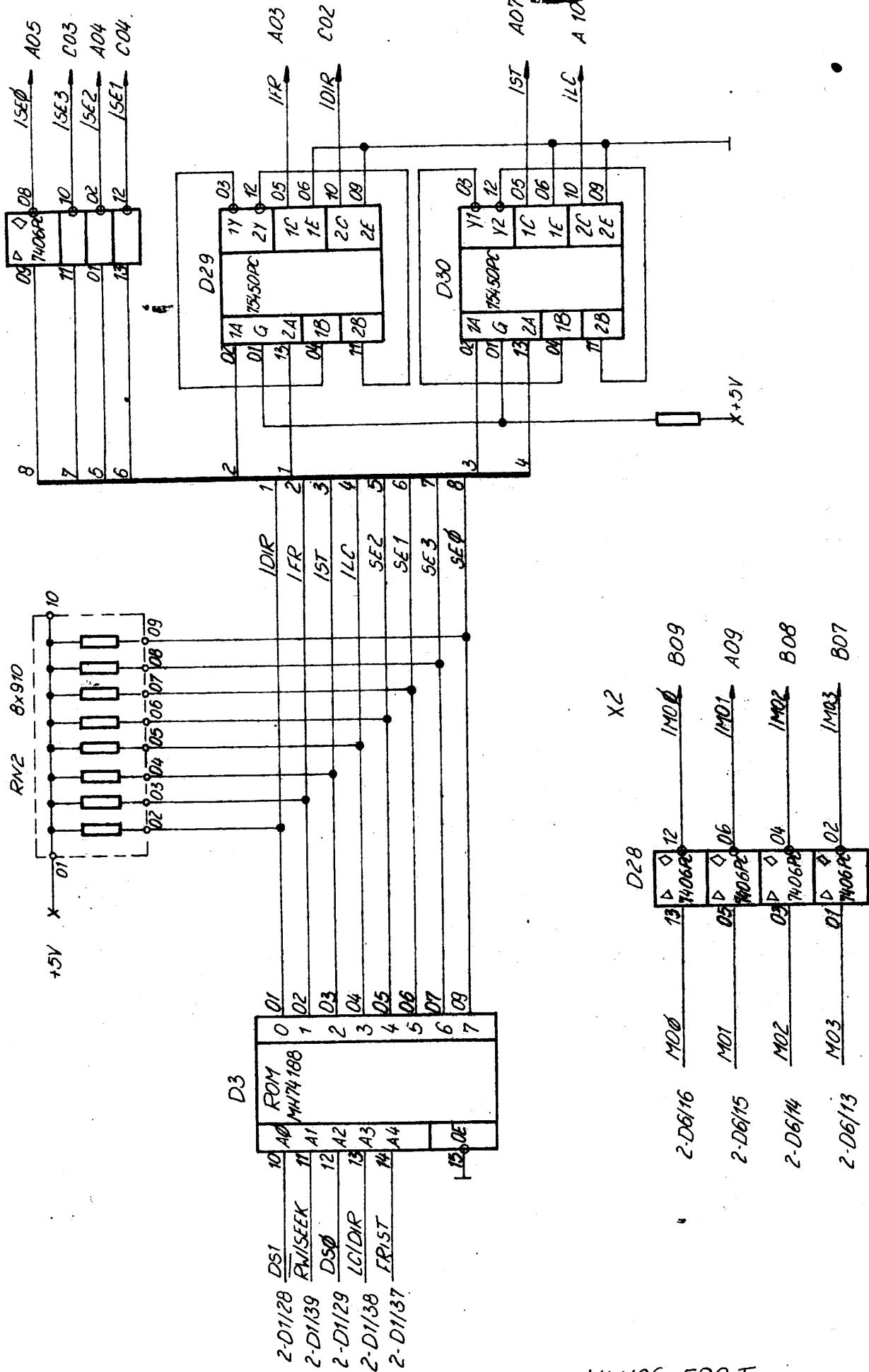

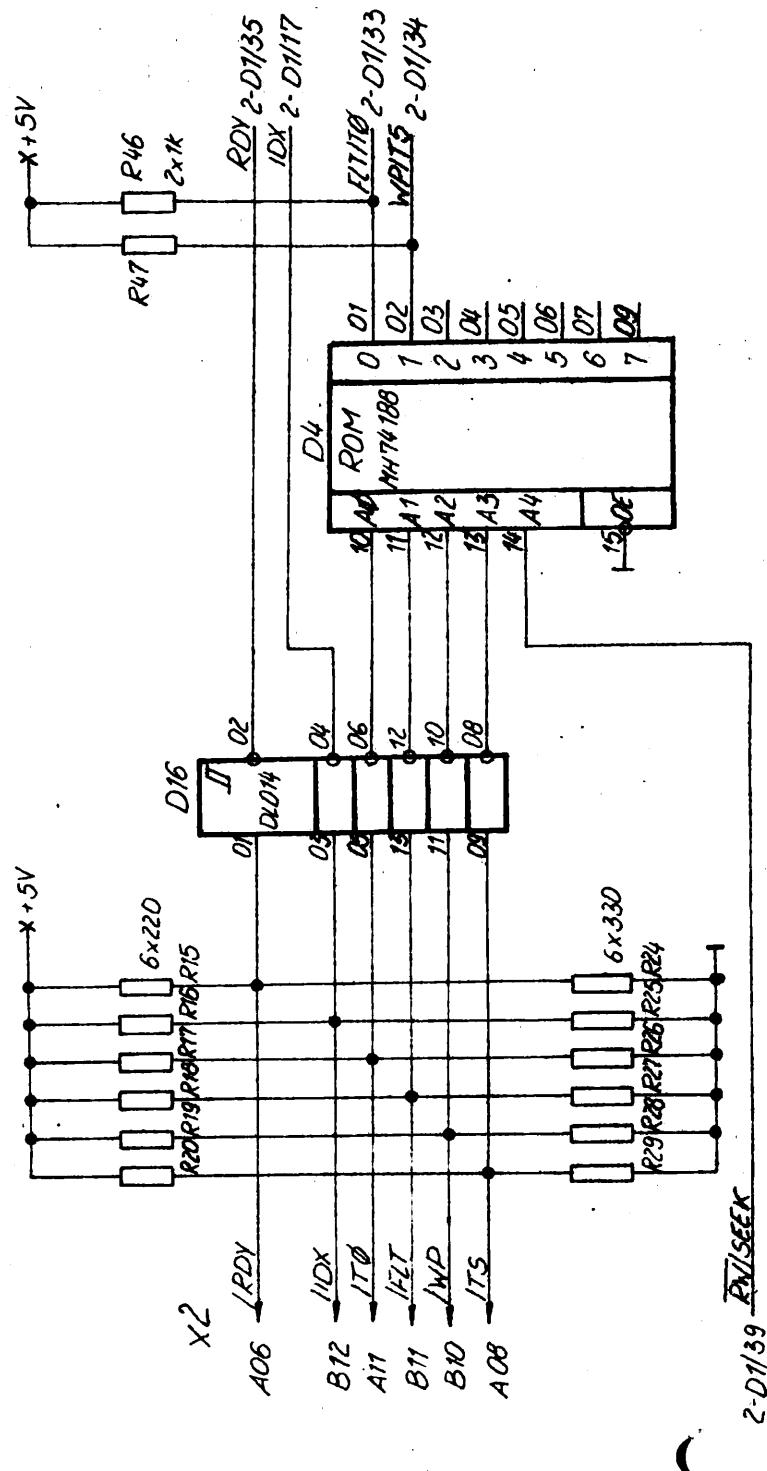

### 3.1.6 Peripherieankopplung

Die Laufwerksteuersignale FR/ST, LC/DIR werden in Abhaengigkeit vom Signal /RW / SEEK und die Laufwerk-Auswahlsignale DSO,DS1 durch den PROM D3 decodiert. Die Ausgangssignale des Decoders D3 werden ueber die Open-Collector-Stufen D29,30 (75450 PC) und D27 (7406 PC) auf den Steckverbinder X2 gefuehrt. Die Signale /FR und /LC werden im Suchmodus, die Signale /DIR und /ST bei einer Schreib-Lese-Operation durchgeschalten. Die Auswahl der einzelnen Laufwerke wird im Zeitmultiplexbetrieb durch die Selectsignale /SE0.../SE3 realisiert.

Die Eingangsleitungen werden durch folgendes Widerstandsnetzwerk angepasst:

Die Quittungssignale der FD-Laufwerke /WP, /TS, /FLT, /T0, /IDX und /RDY werden auf die Eingaenge des Schmitt-Trigger-Empfaengers D16 (DL 014) gefuehrt.

Aus den Laufwerkstatussignalen /WP, /TS, /FLT und /T0 werden im PROM D4 (MH 74188) die Signale FLT/T0 und WP/TS gebildet und in Abhaengigkeit von /RW / SEEK durchgeschalten.

Daraus ergibt sich fuer den Suchmodus die Zuordnung der Signale /T0 und /TS, sowie fuer eine Schreib-Lese-Operation die von /FLT und /WP.

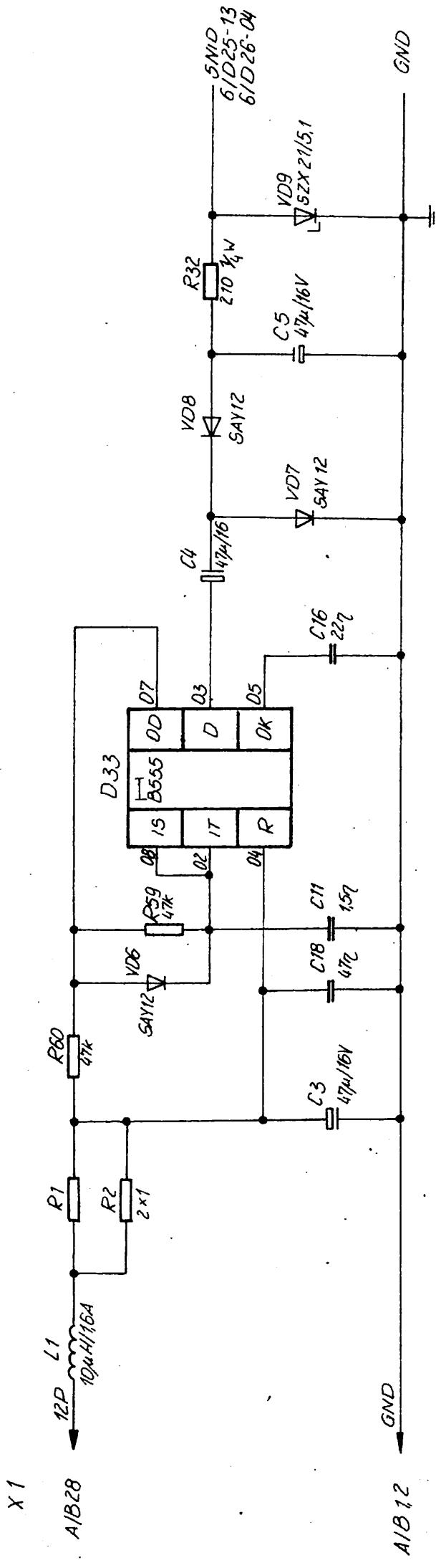

### 3.1.7 Transverter

Zur Versorgung des Operationsverstaerkers D26 (MAA 741), sowie des Leitungsempfaenger-Schaltkreises D25 (75107 PC) der PLL (Phase locked loop) des Datenseparators ist eine negative Betriebsspannung notwendig.

Die Bereitstellung einer negativ gerichteten Versorgungsspannung aus einer vorhandenen positiven Speisespannung erfolgt mittels einer uebertragerlosen Transverterschaltung. Die Spannung -5 V wird intern auf der Baugruppe mit einem im astabilen Betrieb arbeitenden Zeitgeber-Schaltkreis D33 (B 555 D) aus der positiven Betriebsspannung +12 V erzeugt. Der astabile Betrieb erfolgt durch Selbsttriggerung der Schaltung, die durch die Funktion der externen Beschaltung (Widerstaende R 59, R 60; Kondensator C 11) und durch das Verbinden der Pin's 2 und 6 realisiert wird.

Der Schaltkreis D 33 (B 555 D) erzeugt am Ausgang (Pin 3) Rechteckschwingungen mit einer Frequenz von ca. 10 kHz.

Diese Wechselspannung wird durch eine Spannungsverdoppler-Schaltung (Kondensatoren C4, C5; Dioden VD7, VD8) gleichgerichtet, durch die Zenerdiode VD9 und den Vorwiderstand R32 auf die negative Betriebsspannung von ca. -5 V stabilisiert.

## 3.2 Anschlussbedingungen

## 3.2.1 Systembusanschluss

Die Anschlussbedingungen fuer den Systembus ergeben sich aus den Festlegungen des K 1520-Standard's nach der TGL 37 271. Alle von der FDCI-Steuerleinheit genutzten Systembussignale (Adressen-, Steuer- und Datensignale) belasten den Bus mit max. 0,25 mA.

Achtung: Abweichend von der TGL 37 271, erfolgt keine Generierung des /RDY- Signals !

## 3.2.2 Interfaceanschluss D-Laufwerke

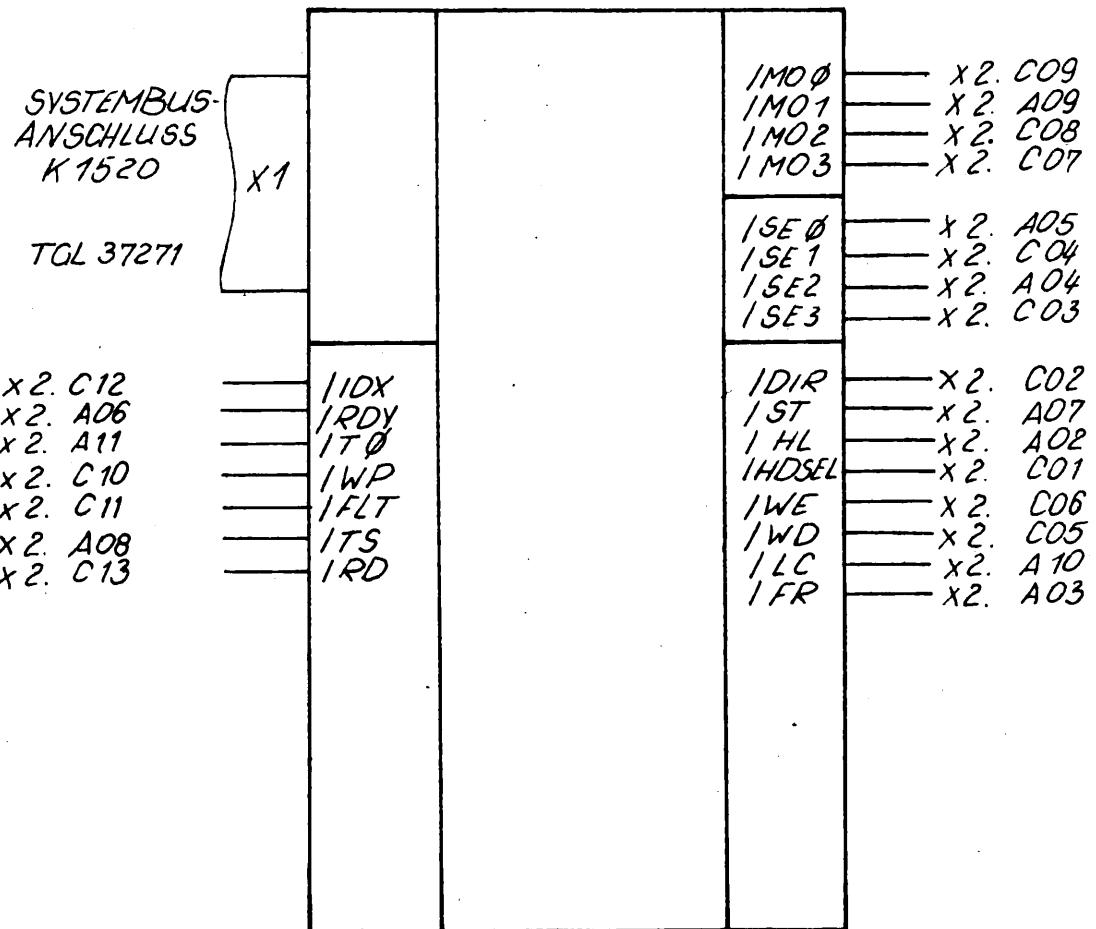

Der Anschluss der Laufwerke erfolgt griffseitig ueber einen indirekten 39-poligen Steckverbinder (X2).

Die Belegung des Signal-Interface-Steckverbinder (X2) ist folgender Tabelle zu entnehmen:

| Kontakt | Signalname | Benennung | Richtung       |                  |     |

|---------|------------|-----------|----------------|------------------|-----|

| 1.6     | 1.2        |           |                |                  |     |

| A 01    | Masse      | Masse     | -              |                  |     |

| A 02    | 4 *        | /HL       | Head Load      | OUT              |     |

| A 03    |            | /FR       | Fault Reset    | OUT              |     |

| A 04    | 14         | /SE2      | Select Drive 2 | OUT              |     |

| A 05    | 10         | *         | /SEO           | Select Drive 0   | OUT |

| A 06    | 34         | *         | /RDY           | Ready            | IN  |

| A 07    | 20         | *         | /ST            | Step             | OUT |

| A 08    |            | /TS       | Two Side       | IN               |     |

| A 09    | 16         | *         | /M01           | Motor on Drive 1 | OUT |

| A 10    |            | /LC       | Low Current    | OUT              |     |

| A 11    | 26         | *         | /T0            | Track 00         | IN  |

| A 12    |            | Masse     | Masse          | -                |     |

| A 13    |            | Masse     | Masse          | -                |     |

| C 01    | 32         | /HDSEL    | Head Select    | OUT              |     |

| C 02    | 18         | *         | /DIR           | Step Direction   | OUT |

| C 03    | 6          |           | /SE3           | Select Drive 3   | OUT |

| C 04    | 12         |           | /SE1           | Select Drive 1   | OUT |

| C 05    | 22         | *         | /WD            | Write Data       | OUT |

| C 06    | 24         | *         | /WE            | Write Enable     | OUT |

| C 07    | 16         | *         | /M03           | Motor on Drive 3 | OUT |

| C 08    | 16         | *         | /M02           | Motor on Drive 2 | OUT |

| C 09    | 16         | *         | /M00           | Motor on Drive 0 | OUT |

| C 10    | 28         | *         | /WP            | Write Protect    | IN  |

| C 11    |            |           | /FLT           | Fault Write      | IN  |

| C 12    | 8          | *         | /IDX           | Index            | IN  |

| C 13    | 30         | *         | /RD            | Read Data        | IN  |

Kontakte B 01...B13 Masseanschluss

#### 4. Inbetriebnahme und Pruefung

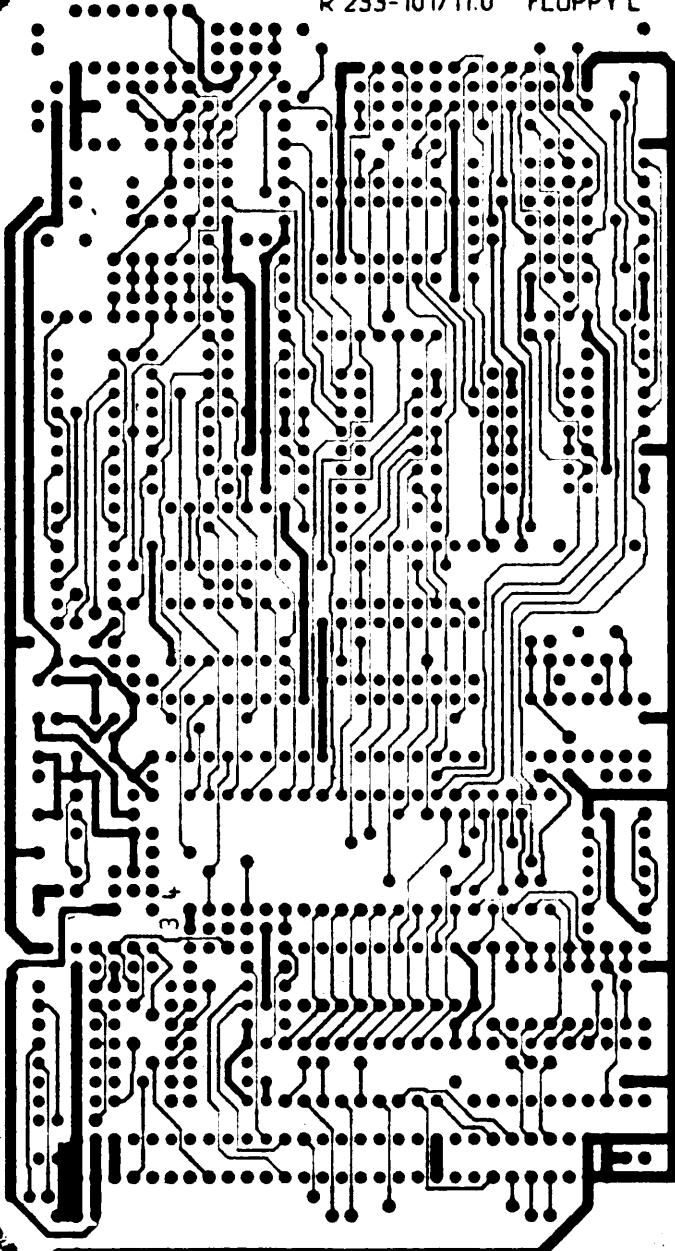

##### 4.1 Vorpruefung der unbestueckten Leiterplatte

Die Leiterbildzeichnungen LBL(4) und LBD(4) zeigen das Layout der beidseitig kaschierten und durchkontaktierten Leiterplatte. Sie ist mittels einer gruendlichen Sichtkontrolle auf Aetzfehler (Fehlverbindungen und Unterbrechungen) zu ueberpruefen.

Eine Isolationsmessung zwischen den Stromversorgungsanschlüssen

X1: A01, B01 - X1: A29, B29

X1: A01, B01 - X1: A28, B28

soll eventuelle Fehlverbindungen (Kurzschluesse) ausschliessen.

##### 4.2 Bestueckungs- und Inbetriebnahmehinweise

Die Baugruppe ist entsprechend dem Bestueckungsplan Bsp(2) aufzubauen.

Die Bestueckung und Inbetriebnahme sollte in der angegebenen Reihenfolge durchgefuehrt werden:

- Einloeten der Steckverbinder X1 und X2, sowie der IC-Fassung fuer den Controllerschaltkreis

- Aufbau und Pruefung des Transverters (siehe Pkt. 4.2.1)

- Aufbau und Pruefung der Lesesteuerung (siehe Pkt. 4.2.2)

- Bestueckung und Kontrolle der Baugruppe

- Elektrische Kontrolle der Baugruppe

- Einstellen der Baugruppenadresse

- Inbetriebnahme im Mikrorechnersystem

##### 4.2.1 Aufbau und Pruefung des Transverters

Der Aufbau des uebertragerlosen Transverters erfolgt gemaeess Bsp(2) und Sp(2) Bl. 9. Vor Ueberpruefung der Funktionsfaehigkeit, sollte eine Sichtkontrolle auf eventuelle Loetbruecken durchgefuehrt werden.

An die Baugruppe wird die Versorgungsspannung von +12V angeschlossen. Die Stromaufnahme des Transverters darf im unbelasteten Zustand 30mA nicht ueberschreiten.

Die Ausgangsspannung betraegt -5V +/-5%.

#### 4.2.2 Aufbau und Pruefung des Datenseparators

Der Aufbau des Datenseparators (Lesesteuerung) erfolgt entsprechend dem Bestueckungsplan Bsp(2) und dem Stromlaufplan Sp(3) El. 6. Es ist dabei auf korrekte und vollstaendige Bestueckung der Lesesteuerung zu achten. Anschliessend ist eine visuelle Kontrolle auf Loetbruecken durchzufuehren.

Die Baugruppe ist an die Versorgungsspannungen 5P, 12P und Masse anzuschliessen. Es ist zu empfehlen, das Vorhandensein der Betriebsspannungen an den IC's zu ueberpruefen.

Die Inbetriebnahme des Datenseparators erfordert einen gewissenhaften Abgleich der Schaltung.

Insbesondere ist dem Abgleich und der Pruefung der PLL-Schaltung grosses Augenmerk zu widmen.

Folgende Messgeraete sind fuer die entsprechenden Messungen erforderlich:

- Frequenzzzaehler

- Oszillograph

- Impulsgenerator

Die Pruefung der Lesesteuerung beginnt mit der Grundeinstellung der VCO-Frequenz. Sie wird mit einem Frequenzzzaehler an MP1 ueberprueft. Die VCO-Frequenz wird mit dem Dickschichteinstellregler R10 auf 2000 kHz  $\pm 1\%$ , bei einem Lesesignal /RD = H-Potential, eingestellt.

#### Statische Pruefung der PLL-Schaltung:

An den Steckverbinder X2:013 (/RD) ist der Impulsgenerator anzuschliessen und ein /RD-Signal mit folgender Impulsform einzustellen.

Mit dem Oszillograph sind das /RD-Signal und die VCO-Frequenz zu kontrollieren.

Oszillographeneinstellung: Kanal A /RD-Signal

Kanal B VCO-Takt

Zeitbasis 0,5  $\mu s$ /Teil.

Die PLL ist eingerastet, wenn die VCO- und /RD-Frequenz synchron laufen, d.h. jeder 4. VCO-Taktimpuls muss innerhalb einer /RD-Information liegen (siehe Abb.).

X2:013

Durch Verändern der /RD-Frequenz lässt sich der Halte- und Ziehbereich, die bereits in Pkt. 3.1.4.1 als wichtige Kenngrößen einer PLL beschrieben wurden, annähernd bestimmen.

Die Prüfung der Sonderbaustufe (Impulsverzögerung/-verkürzung) soll Aussagen darüber machen, wie die Datenbits innerhalb eines Datenfensters liegen. Der ideale Übertragungspunkt liegt in der Mitte des DW. In der verwendeten Schaltung wurde eine Verzögerungszeit von ca. 250...300 ns festgelegt (siehe Abb. 12). Die Datenimpulsbreite des RDATA-Signals sollte ca. 80 ns betragen.

Ermerkung: Die Grundeinstellung der VCO-Frequenz und die Prüfung der PLL-Schaltung sind generell nur durchzuführen, wenn die Baugruppe nicht mit dem Controllerschaltkreis bestückt ist.

#### 4.3 Prüfung und Inbetriebnahme der bestückten STE

##### 4.3.1 Prüfung der bestückten Baugruppe

Nach erfolgter Prüfung des Transverters und Datenseparators ist die Baugruppe vollständig zu bestücken. Die Leiterplatte wird anschliessend auf korrekte Bestückung gemäss dem Bestückungsplan Bsp(2) überprüft. Insbesondere sind die richtige Lage der Bausteine, sowie der Elektrolytkondensatoren zu kontrollieren.

Vor Inbetriebnahme ist eine nochmalige Sichtkontrolle auf eventuell vorhandene Loetbrüecken durchzuführen.

#### 4.3.2 Stromaufnahme der Baugruppe

Vor der Funktionsueberpruefung der Baugruppe ist die Stromaufnahme zu messen. Der Controller-Schaltkreis ist nicht gesteckt. Die STE wird an die Versorgungsspannungen 5P, 12P und Masse angeschlossen. Die Stromaufnahme der Versorgungsspannung 5P betraegt etwa 850 mA und bei 12P ca. 40 mA. Anschliessend sind alle angegebenen Frequenzen (Grundtakt C, Schreibtakt WRCLK und VCO-Takt) zu kontrollieren und ggf. zu korrigieren.

Bei gestecktem Controller-Schaltkreis und angeschlossenem FD-Laufwerk betraegt die Stromaufnahme ca. 300 mA bei 5P und etwa 40 mA bei 12P.

| Messbedingung     | Stromaufnahme              |

|-------------------|----------------------------|

| Baugruppe ohne D1 | 5P / 850 mA<br>12P / 40 mA |

| Baugruppe mit D1  | 5P / 300 mA<br>12 / 40 mA  |

Um bei der Inbetriebnahme der FDCI-Steuereinheit in einem Mikrorechnersystem eventuelle Buskonflikte zu vermeiden, ist es zweckmaessig, die Busanschlussleitungen der Baugruppe auf ihren Zustand zu ueberpruefen.

Der Datenbustreiber D8 (DS 8206) muss inaktiv sein. Alle TTL-Eingaenge muessen unbestimmtes Potential fuhren.

#### 4.4 Erstinbetriebnahme

Die Inbetriebnahme der STE beginnt mit dem Einstellen der Baugruppenadresse KW 0...3 (siche Pkt. 3.1.1.2). Im NANOS-Baugruppensystem ist sie mit 90H festgelegt.

Die Funktionspruefung der Baugruppe erfolgt in einem Mikrorechnersystem. Das FD-Laufwerk wird ueber einen Adapter an die Steuerkarte angeschlossen. Dabei ist zu beachten, dass das Laufwerk eigene Versorgungsspannungen (5P, 12P) benoetigt.

Nach dem Einschalten der Stromversorgung bzw. einem POWER-ON-RESET meldet sich das Monitorprogramm, die FDCI-Steuereinheit befindet sich im Grundzustand.

Mit Hilfe des Monitors koennen zunaechst einfache Grundfunktionen der Baugruppe getestet werden (siehe folgende Beispiele).

E/A-Portadresse 92H : Laden Laufwerkfunktionsregister

- Ansteuerung Antriebssysteme der Laufwerke (Signale M0 0...3)

- Taktschaltung (C, WRCLK, PLL-Rasterfrequenz)

- usw.

Ausgabe des Datenbyte 01H auf I/O-Port 92H :

Im Laufwerkfunktionsregister D6 wird das Bit 0 (Signal MINI) gesetzt. Mit dem Zaehler werden die Frequenzen C, WRCLK und die PLL-Rasterfrequenz ueberprueft. Sie muessen folgende Werte annehmen :

|                          |          |

|--------------------------|----------|

| - Basistakt              | 4000 kHz |

| - Schreibtakt            | 500 kHz  |

| - Rasterfrequenz der PLL | 500 kHz  |

Ausgabe des Datenbyte 09H auf I/O-Port 92H :

Die Bits 0 (Signal MINI), und 3 (Signal M0 0) von D6 werden gesetzt. Die Frequenzen muessen mit denen im ersten Beispiel uebereinstimmen. Gleichzeitig wird der Antriebsmotor des Laufwerks 0 eingeschaltet.

E/A-Portadresse 94H : Hauptstatusregister des FDC

- Abfrage des Hauptstatusregisters

Abfrage Inhalt des I/O-Port 94H :

Das Hauptstatusregister des Controllers wird abgefragt. Im fehlerfreien Fall muss der Inhalt des Ports 00H betragen. Das Bit D7 (RQH) ist gesetzt, d.h. dass das Datenregister des Controllers bereit ist Daten zu senden bzw. zu empfangen.

E/A-Portadresse 95H : Datenregister des FDC

- Initialisierung

Auswahl der Laufwerke (Signale /SE0...3)

Positionieren Schreib-/Lesekopf auf Spur 0

Positionieren auf vorgewaehlte Spur XX

Ausgabe des Kommando Recalibrate (Spur 0) auf I/O-Port 95H :

2-Byte Befehl: 07H KMD Spur 0

00H Laufwerk 0

Das Laufwerk 0 wird ausgewaehlt und der Schreib-/Lesekopf auf die Spur 0 positioniert.

Es koennen die Signale Index (/IDX) und Spur 0 (/T0) oszillographisch ueberprueft werden.

Ausgabe des Kommando SEEK (Suchen) auf I/O-Port 95H :

3-Byte Befehl: 0FH Suchen

00H Laufwerk 0

00H Spur 8

Das Laufwerk 0 wird ausgewaehlt und der Schreib-/Lesekopf auf die Spur 8 positioniert.

Achtung: Bei den Grundpruefungen mit dem Testmonitor, werden die Laufwerkparameter (Steprate, Kopflade- und -entladezeit) nicht an den FDC uebergeben, so dass die Positionierkommandos "hart" ausgefuehrt werden.

#### 4.5 Pruefprogramm

Eine Aussage ueber die volle Funktionstuechtigkeit der Baugruppe kann erst nach Pruefung des dynamischen Verhaltens gemacht werden.

Ein von SCHEFE angegebenes Disketteninitialisierungsprogramm FORMAT wird zum Funktionsnachweis verwendet (Listing siehe Anlage).

Die Minidiskette wird durch Beschreiben jeder Spur von Anfang bis Ende ohne Unterbrechung initialisiert. Der Anfang und das Ende jeder Spur ist durch den Indeximpuls definiert.

Programmbeschreibung: Das Formatieren der Diskette erfolgt mit dem Kommando FORMAT A TRACK. Nach Bereitstellung der ID-Feldinformationen (Spur-Nr., Seiteninformation, Sektor-Nr., Blocklaenge) wird das Fuehlbyte ausgegeben. Dieser Vorgang erfolgt fuer jeden Sektor der Spur, ein anschliessendes Kontrollesen bewirkt die Ausgabe der fehlerhaften Spur. Danach wird die Initialisierung der Diskette fortgefuehrt.

Wird die Formatierung der Diskette erfolgreich abgeschlossen, kann die Baugruppe in einem diskettenorientierten Mikrorechnersystem eingesetzt und getestet werden.

Bei einem negativen Testergebnis, sind die Statusbytes des FDC auszuwerten, um somit die Fehlerursache einzugrenzen (siehe Beschreibung FDC 3272 D).

Das Pruefprogramm FLOTEST.TSL (in Bearbeitung) erweitert die individuellen Pruefmoeglichkeiten durch die Implementierung entsprechender Befehle.

Inhalt des Testprogramm:

- Formatieren einer Diskette und Kontrollesen

(nach jedem fehlerfrei gelesenen Sektor wird auf dem Monitor, als Bedienerinformation, ein Stern ausgegeben)

- Eine Erweiterung der individuellen Pruefmoeglichkeiten wird mit der Implementierung der Lese- und Schreibkommandos (Read Data, Read ID und Write Data) erreicht.

Beschreibung Pruefprogramm FLOTEST.TSL :

Zunaechst wird die FDCI-Steuerinheit durch das Signal /RESET in den Grundzustand versetzt.

Das Pruefprogramm FLOTEST.TSL wird aufgerufen und geladen. Ausgehend von einem Menueprogramm, werden die einzelnen Teilprogramme ausgewaehlt und abgearbeitet.

|                |               |                                                                    |

|----------------|---------------|--------------------------------------------------------------------|

| Teilprogramme: | - FLOTEST.INI | Diskette initialisieren und Kontrollesen (CRC-Pruefbyte Vergleich) |

|                | - FLOTEST.WR  | Beschreiben eines Sektor mit Schreibdaten                          |

|                | - FLOTEST.RD  | Lesen eines Sektor                                                 |

|                | - FLOTEST.ID  | Lesen ID-Feld eines Sektor                                         |

|                | - FLOTEST.PAR | Modifizieren Laufwerksparameter                                    |

Mit dem Start eines der Testprogramme (ausser FLOTEST.PAR) werden die Kenndaten der Laufwerke (Steprateneinstellung, Kopflade- und Kopfentladzezeitkonstante) durch den Befehl SPECIF an den Controller uebergeben und in den dafuer vorsehenen Registern gespeichert. In das Laufwerkfunktionsregister werden Parameter, wie Ansteuersignale der Laufwerk-antriebe, Laufwerkstyp usw. gespeichert.

Danach wird mit dem Befehl RECALIBRATE der Schreib-/Lesekopf des selektierten Laufwerks auf die Spur 0 positioniert.

Der weitere Programmablauf, der im folgenden Abschnitt beschrieben wird, ist nur fuer FLOTEST.INI relevant.

Das Formatieren der Diskette erfolgt mit dem Kommando FORMAT A TRACK. Mit diesem Befehl wird immer nur eine Spur der Diskette formatiert, wobei fuer jeden Sektor die Para-

meter (ID-Feldinformationen, wie Seiteninformation, Spur- und Sektornummer, Blocklaenge und das Fuellbyte) von der ZRE an den Controller zu uebergeben sind.

Dieses Kommando ist demzufolge fuer jede Spur der Diskette zu wiederholen und abzuarbeiten. Nach Abschluss dieser Operation erfolgt anschliessend ein Kontrollesen der aufgezeichneten Daten (CRC-Pruefbyte Vergleich). Der Lesevorgang wird durch den Befehl Read Data ausgelöst. Nach jedem fehlerfrei gelesenen Sektör erscheint auf dem Bildschirm ein Stern, der der optischen Kontrolle des Bedieners dient.

Tritt wachrend des Lesens ein Fehler auf, so wird der Vorgang abgebrochen, der Inhalt der Statusbytes des Controllers auf dem Bildschirm angezeigt und entsprechend kommentiert. Anschliessend kann in das Menueprogramm zurueckgekehrt werden. Verlief die Initialisierung der Diskette fehlerfrei, erfolgt automatisch der Ruecksprung ins Menueprogramm.

Der Bediener hat die Moeglichkeit, durch den Aufruf eines der Teilprogramme FLOTTEST.WR, FLOTTEST.RD und FLOTTEST.ID individuell Pruefungen (Schreiben und Lesen von Daten, Lesen ID-Marke) vorzunehmen. Nach Abschluss einer Operation werden die Statusbytes des FDC auf dem Bildschirm angezeigt und ebenfalls kommentiert.

Das Teilprogramm FLOTTEST.PAR ermoeglicht FD-Laufwerke, deren Kennwerte von den softwaremaessig, voreingestellten Parametern abweichen, anzuschliessen. Die Kennwerte der Laufwerke (Steprateneinstellung, Kopflade- und -entladeseit) werden im Spezifikationsbyte aktualisiert. Die Parameter sind den Laufwerkbeschreibungen zu entnehmen.

## 5. Anwenderhinweise

Die Anschlussseinheit wurde so konzipiert, dass der Anschluss unterschiedlicher Laufwerke moeglich ist. Sollen andere, als die aufgefuehrten Laufwerke eingesetzt werden, ist zu pruefen, inwieweit diese die Bedingungen erfüllen. Es ist zu empfehlen, vor Inbetriebnahme der Laufwerke, die technische Beschreibung aufmerksam zu lesen und die entsprechenden Herstellerhinweise zu beachten.

Ein wesentliches Kriterium beim Anschluss von Laufwerken an die Baugruppe stellt die Bildung des Signals /RDY dar.

Achtung: Kommen Laufwerke zum Einsatz, die das Signal /RDY nicht generieren, ist fuer die FDCI-Steuereinheit dieses Signal extern bereitzustellen!

Die folgenden Laufwerkstypen koennen bei Verwendung entsprechender Adapterkabel ohne Probleme an die Anschlussseinheit angeschlossen werden.

- Robotron K 5600.10/20 OEM

(zu beachten: Signal /HL Schalter DS 2/6 offen, X 29/30 gebrueckt)

- MFS 1.6 TEAC FD-55PV-13-U

(notwendige Bruecken auf dem Laufwerk: DS 0, FG, RY, U2)

Der Anschluss der Laufwerke Robotron K 5600.10/20 an die Steuereinheit, erfordert eine hardwaremaessige Aenderung auf dem Laufwerk.

( Signal /HL : Baustein 23 / D 204

Leiterzug zum Eingang 11 auftrennen,

Bruecke von Pin 11 auf Masse legen)

Die Software fuer die FDCI-Steuereinheit dient der Anbindung von Floppy-Disk- Laufwerken in ein CP/M- kompatibles Betriebssystem, unterstuetzt den Betrieb von Minilaufwerken (5 1/4-Zoll) im MFM-Aufzeichnungsverfahren und den von Standardlaufwerken (8-Zoll) im FM-Aufzeichnungsverfahren. Der Datentransfer zwischen dem Prozessor und dem Controller erfolgt im Polling-Mode.

Entsprechende Hinweise sind der Dokumentation "Softwarebeschreibung CP/M- Einbindung der FDCI-Steuereinheit" zu entnehmen.

Steuersignaldecodierung

PROM-Daten D2

Adresszuordnungen:

| PIN | ADRESSE | SIGNAL |

|-----|---------|--------|

| 10  | A0      | /STB*  |

| 11  | A1      | RD     |

| 12  | A2      | WR     |

| 13  | A3      | /AB0   |

| 14  | A4      | RESET  |

Auswahlsignalzuordnung:

| PIN | Steuereingang | Signal |

|-----|---------------|--------|

| 15  | /OE           | /ASW-S |

Datenzuordnungen:

| PIN | BIT | SIGNAL |

|-----|-----|--------|

| 01  | D0  | DIR    |

| 02  | D1  | A0     |

| 03  | D2  | n.b.   |

| 04  | D3  | /RD    |

| 05  | D4  | /WR    |

| 06  | D5  | /STB   |

| 07  | D6  | n.b.   |

| 09  | D7  | n.b.   |

PROM-Inhalt (Hexadezimal):

3F 3F 3F 36 3F 2F 3F 3F 3D 3D 3D 3D 34 0D 3D 3D 3D

3D 3D 3D 3D 3D 3D 3D 3D 3F 3F 3F 3F 3F 3F 3F 3F

Laufwerksteuersignale

PROM-Daten D3

Adresszuordnungen:

| PIN | ADRESSE | SIGNAL     |

|-----|---------|------------|

| 10  | A0      | DS1        |

| 11  | A1      | /RW / SEEK |

| 12  | A2      | DS0        |

| 13  | A3      | LC/DIR     |

| 14  | A4      | FR/ST      |

Auswahlsignalzuordnung:

| PIN | Steuereingang | Signal |

|-----|---------------|--------|

| 15  | /OE           | GND    |

Datenzuordnungen:

| PIN | BIT | SIGNAL |

|-----|-----|--------|

| 01  | D0  | /DIR   |

| 02  | D1  | /FR    |

| 03  | D2  | /ST    |

| 04  | D3  | /LC    |

| 05  | D4  | SE2    |

| 06  | D5  | SE1    |

| 07  | D6  | SE3    |

| 09  | D7  | SE0    |

PROM-Inhalt (Hexadezimal):

8F 1F 8F 1F 2F 4F 2F 4F 87 17 8E 1E 27 47 2E 4E

8D 1D 8E 1B 2D 4D 2B 4B 85 15 8A 1A 25 45 2A 4A

Laufwerkstatussignale

PROM-Daten D4

Adresszuordnungen:

| PIN | ADRESSE | SIGNAL     |

|-----|---------|------------|

| 10  | A0      | T0         |

| 11  | A1      | FLT        |

| 12  | A2      | WP         |

| 13  | A3      | TS         |

| 14  | A4      | /RW / SEEK |

Auswahlsignalzuordnung:

| PIN | Steuereingang | Signal |

|-----|---------------|--------|

| 15  | /OE           | GND    |

Datenzuordnungen:

| PIN | BIT | SIGNAL |

|-----|-----|--------|

| 01  | D0  | FLT/T0 |

| 02  | D1  | WP/TS  |

| 03  | D2  | n.b.   |

| 04  | D3  | n.b.   |

| 05  | D4  | n.b.   |

| 06  | D5  | n.b.   |

| 07  | D6  | n.b.   |

| 09  | D7  | n.b.   |

PROM-Inhalt (Hexadezimal):

00 00 01 01 02 02 03 03 00 00 01 01 02 02 03 03

00 01 00 01 00 01 00 01 02 03 02 03 02 03

## Kurzzeichenuebersicht

|     |                                                                    |

|-----|--------------------------------------------------------------------|

| FDC | Floppy-Disk-Controller (FDC-Schaltkreis)                           |

| FM  | Frequenzmodulation (Aufzeichnungsverfahren)                        |

| MFM | modifiziertes FM-Aufzeichnungsverfahren                            |

| PLL | Phase locked loop (Phasenregelschleife)                            |

| VCO | Voltage controlled oscillator<br>(spannungsgesteuerter Oszillator) |

## Systembussignale

|       |                                        |

|-------|----------------------------------------|

| AB... | Adressbus                              |

| DB... | Datenbus                               |

| M1    | Maschinenbefehlszyklus (low-aktiv)     |

| RD    | Steuersignal Lesen (low-aktiv)         |

| RESET | Ruecksetzsignal (low-aktiv)            |

| IODI  | Eingabe/Ausgabe abschalten (low-aktiv) |

| IORQ  | Eingabe/Ausgabe anfordern (low-aktiv)  |

| WR    | Steuersignal Schreiben (low-aktiv)     |

## Baugruppeninterne Signale

|        |                                                                                    |

|--------|------------------------------------------------------------------------------------|

| ADD    | Baugruppenselectsignal (high-aktiv)                                                |

| ASW-S  | Bausteinselect-Sammelsignal (low-aktiv)                                            |

| AO     | Daten-/Statusregisterauswahl                                                       |

| C      | Takt ,Grundtakt fuer Controller                                                    |

| CS     | Auswahl Controllerschaltkreis                                                      |

| DACK   | DMA-Freigabe (low-aktiv)                                                           |

| DB...  | Datenbus                                                                           |

| DIR    | Steuerung der Datenflussrichtung (high-aktiv)                                      |

| DRQ    | Daten DMA-Anforderung (high-aktiv)                                                 |

| DS 0,1 | Laufwerksauswahl (gemultiplext)                                                    |

| DW     | Datenfenster                                                                       |

| FLT/T0 | Steuersignal FD:Fehler Schreibsteuerung/<br>Schreib-/Lesekopf auf Spur 0           |

| FR/ST  | Steuersignal FD:FF-Fehler Schreibsteuerung<br>ruecksetzen/<br>Positionierschritt   |

| INT    | Interruptanforderung (high-aktiv)                                                  |

| LC/DIR | Steuersignal FD:Schreibstromverringerung/<br>Richtung Positionierschritt           |

| MINI   | Steuersignal Taktumschaltung<br>(low-Pegel Standard-LW,<br>high-Pegel Mini-LW)     |

| MFM    | MFM-Betriebsart<br>(low-Pegel FM-Datenaufzeichnung<br>high-Pegel MFM-Aufzeichnung) |

| PSE    | Freigabesignal Praecompensation (high-aktiv)                                       |

| PS 0,1 | Praecompensationssignale                                                           |

| RESET  | Ruecksetzsignal Controller (high-aktiv)                                            |

| RD     | Steuersignal Lesen - FDC (low-aktiv)                                               |

| RDATA  | Lesesignal - Lesedaten vom FD                                                      |

|         |                                                                                   |

|---------|-----------------------------------------------------------------------------------|

| RW/SEEK | Auswahl Betriebsart FD:<br>(low-Pegel Lese-/Schreibmodus<br>high-Pegel Suchmodus) |

| STB     | Speichersignal (high-aktiv)                                                       |

| TC      | FDC-Abruchsignal (high-aktiv)                                                     |

| VCo     | Freigabesignal Lesesteuerung (high-aktiv)                                         |

| WR      | Steuersignal Schreiben - FDC (low-aktiv)                                          |

| WRCLK   | Schreibtakt                                                                       |

| WRDATA  | Schreibdaten zum FD                                                               |

## Laufwerksignale

|       |                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------|

| DIR   | Richtungssteuerung Schreib-/Lesekopf des FD<br>(low-Pegel entgegen Spur 0<br>high-Pegel in Richtung Spur 0) |

| FLT   | Fehler in der Schreibsteuerung (low-aktiv)                                                                  |

| FR    | FF-Fehler in der Schreibsteuerung rücksetzen<br>(low-aktiv)                                                 |

| HDSEL | Auswahl der Schreib-/Lesekopfe<br>(low-Pegel Auswahl Kopf 0 /<br>high-Pegel Auswahl Kopf 1)                 |

| HL    | Ansteuersignal Kopflademagnet (low-aktiv)                                                                   |

| IDX   | Indexsignal (low-aktiv)                                                                                     |

| LC    | Schreibstromverringerung (low-aktiv)                                                                        |

| MO... | Einschalten der Laufwerksantriebe (low-aktiv)                                                               |

| RD    | Lesesignal vom FD / serielles Daten-Takt-<br>Gemisch                                                        |

| RDY   | Bereitschaftssignal des FD (low-aktiv)                                                                      |

| SE... | Auswahlsignale der Laufwerke (low-aktiv)                                                                    |

| ST    | Schrittimpuls beim Positionieren (low-aktiv)                                                                |

| TS    | Seitenstatus im Suchbetrieb, nur bei Doppel-<br>kopflaufwerken relevant (low-aktiv)                         |

| TO    | Schreib-/Lesekopf auf Spur 0                                                                                |

| WD    | Schreibdaten zum FD, serielles Daten-Takt-<br>Gemisch                                                       |

| WE    | Schreiberlaubnis (low-aktiv)                                                                                |

| WP    | Schreibschutz (low-aktiv)                                                                                   |

1 2 3

K 1520 - SYSTEMBUS

D

| Halbzeug/Werkstoff        |            |            |      | zul. Abw. für Maße<br>ohne Toleranzang. |

|---------------------------|------------|------------|------|-----------------------------------------|

| Benennung                 |            |            |      | Maßstab                                 |

| Funktionsgruppenplan FDC1 |            |            |      | Bl. Anz. Bl. Nr.                        |

| ÄZ                        | Mitteilung | Datum      | Name |                                         |

| Bearb.                    | Datum      | Name       |      |                                         |

| Konstr.                   |            |            |      |                                         |

| Technol.                  |            |            |      |                                         |

| Stand.                    |            |            |      |                                         |

| Zeichnungs-Nr.            |            |            |      |                                         |

| R233- 101/11.0 FP (4)     |            |            |      |                                         |

| Ers. für                  |            | Ers. durch |      |                                         |

|                           |            |            |      | Abt. R                                  |

## NANOS-FDCI

## TAKT GENERATOR

R233 - 101/110 Sp(4)

Bl. 3

NANOS-FDCI

Schreibtaktgenerierung

WR CLK

2/D14-11 C

1/MFM

R 233-101/110 Sp(4)

Bl. 4

## Präcompensation-Schaltung

R233-101/11.0 Sp(4)

B1.5

NANOS-FDC I

Dekodierung Auswähl- u. Steuersignale

TREIBERSTUFEN

D-Motoransteuerung, Auswähl- und

Steuersignalen (p)

R233-101/11.0 SP (4)

NANOS: FOCT

## TRIEBERSTUFEN (FD-Daten-, Steuer- und Statussignale)

R 2333-101; 110 SP(4) *BL.8*

## Stromversorgung 5NID

R 233-101/110 Sp(4)

B1.9

1 2 3 4

A

R 233-101/11.0 FLOPPY L

B

C

D

Stand.

Halbzeug/Werkstoff

zul. Abw. für Maße

ohne Toleranzang.

TGL 250 16/02

Benennung

Maßstab

BL Anz. Bl. Nr.

Leiterplatte

1:1

1 1

Leiterbildzeichnung LS

Masse

AZ Mitteilung Datum Name

Zeilahmungs-Nr.

IHS Warnemünde/

Wustrow

Bearb.

R 233 - 101/11.0 LBL (4)

Konstr.

Technol.

Abt. R

Ers. für

Ers. durch

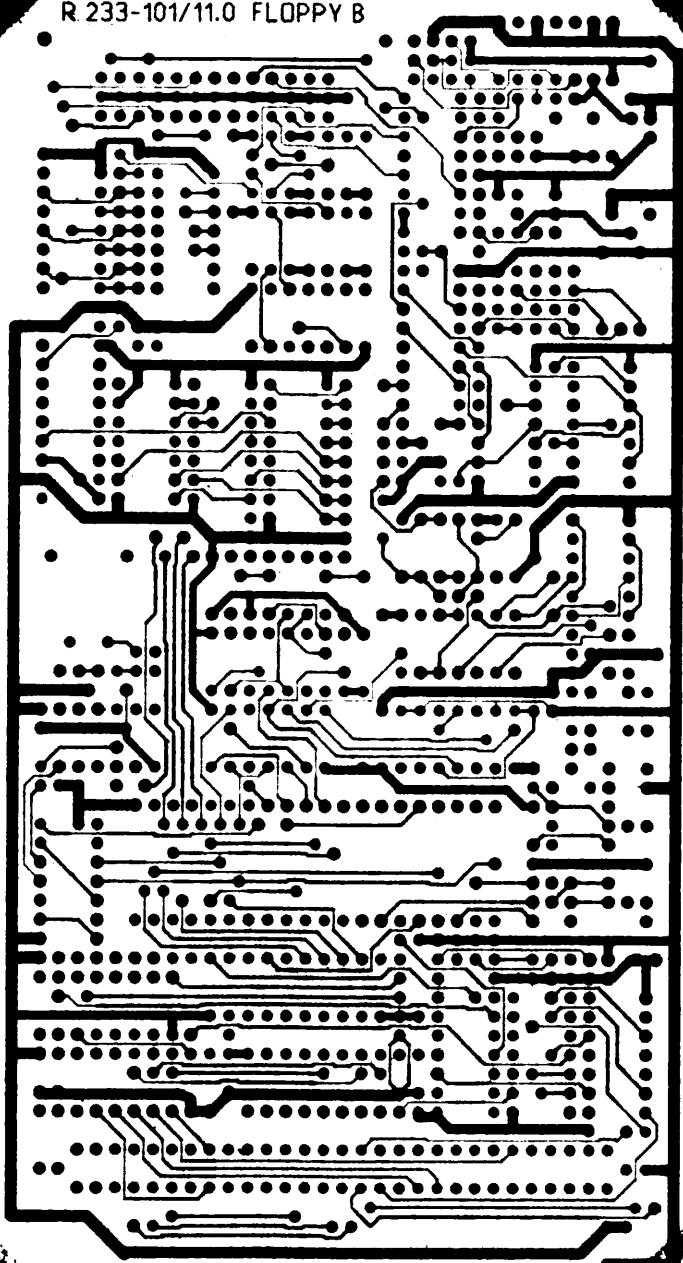

|                 |                   |              |             |                            |                                         |                            |

|-----------------|-------------------|--------------|-------------|----------------------------|-----------------------------------------|----------------------------|

|                 |                   |              |             | Halbzeug/Werkstoff         | zul. Abw. für Maße<br>ohne Toleranzang. |                            |

|                 |                   |              |             |                            | TGL 250 16/02                           |                            |

| D               |                   |              |             | <b>Benennung</b>           | <b>Maßstab</b>                          | <b>Bl. Aaz. Bl. Nr.</b>    |

|                 |                   |              |             | Leiterplatte               | 1:1                                     | 11                         |

| <b>AZ</b>       | <b>Mitteilung</b> | <b>Datum</b> | <b>Name</b> | <b>Leiterbildzeichnung</b> | <b>BS</b>                               | <b>Masse</b>               |

|                 | Datum             |              | Name        | Zeichnungs-Nr.             |                                         |                            |

| <i>Bearb.</i>   |                   |              |             |                            |                                         | IHS Warnemünde/<br>Wustrow |

| <i>Konstr.</i>  |                   |              |             |                            |                                         |                            |

| <i>Technol.</i> |                   |              |             |                            |                                         |                            |

| <i>Stand.</i>   |                   |              |             | Ers. für                   | Ers. durch                              | Abt. : R                   |

| 1               |                   |              |             | 2                          | 3                                       | 4                          |

## Schaltteilliste

| Lfd. Nr.                 | Pos. Nr.         | Stck. | Benennung | Sach-Nr.                        | Bemerkung         |

|--------------------------|------------------|-------|-----------|---------------------------------|-------------------|

| Integrierte Schaltkreise |                  |       |           |                                 |                   |

| 1                        | D 1              | 1     | U 8272 D  | 1378744000 827221<br>TGL .. ... | i 8272<br>μPD 765 |

| 2                        | D2, D3,<br>D4    | 3     | MH 74138  | 1378771009 741081               |                   |

| 3                        | D5               | 1     | DS 8205 D | 1378771009 820513<br>TGL 39 366 |                   |

| 4                        | D6               | 1     | DS 8202 D | 1378773004 828216<br>TGL 42 623 |                   |

| 5                        | D7               | 1     | DS 8283 D | 1378773004 828312<br>TGL 42 623 |                   |

| 6                        | D8               | 1     | DS 8286 D | 1378773004 823654<br>TGL 42 322 |                   |

| 7                        | D13              | 1     | MH 74S04  | 1378773004 074055               |                   |

| 8                        | D9, D10          | 2     | DL 000 D  | 1378774007 000128<br>TGL 39 865 |                   |

| 9                        | D11, D12         | 2     | DL 004 D  | 1378774007 004065<br>TGL 39 865 |                   |

| 10                       | D14              | 1     | DL 008 D  | 1378774007 008031<br>TGL 39 865 |                   |

| 11                       | D15              | 1     | DL 011 D  | 1378774007 011126<br>TGL 39 865 |                   |

| 12                       | D16              | 1     | DL 014 D  | 1378774007 014087<br>TGL 43 206 |                   |

| 13                       | D17, D18,<br>D19 | 3     | DL 074 D  | 1378774007 074020<br>TGL 39 865 | KM555 TM2         |

| 14                       | D20              | 1     | DL 085 D  | 1378774007 085...<br>TGL .. ... | K 555 CR1         |

|    |                       |   |          |                                           |

|----|-----------------------|---|----------|-------------------------------------------|

| 15 | D21                   | 1 | DL 123 D | 1378774007 113093<br>TGL 43 203           |

| 16 | D22                   | 1 | DL 175 D | 1378774007 175016 KM555 TN8<br>TGL 43 293 |

| 17 | D23                   | 1 | DL 193 D | 1378774007 193054<br>TGL 43 204           |

| 18 | D24                   | 1 | DL 253 D | 1378774007 253010<br>TGL 43 295           |

| 19 | D25                   | 1 | 75107 PC | 1378771009 751001                         |

| 20 | D27, D28              | 2 | 7406 PC  | 1378771009 740652                         |

| 21 | D29, D30,<br>D31, D32 | 4 | 75450 PC | 1378771009 754528                         |

| 22 | D33                   | 1 | B 555 D  | 1378771009 555086<br>TGL 34 160           |

## Operationsverstaerker

|    |     |   |         |                   |

|----|-----|---|---------|-------------------|

| 23 | D26 | 1 | MAA 741 | 1378761003 741073 |

|----|-----|---|---------|-------------------|

## Transistor bipolar

|    |     |   |          |                                            |

|----|-----|---|----------|--------------------------------------------|

| 24 | VT1 | 1 | SC 307 c | 1378231109 307023 KT 326 5 H<br>TGL 37 871 |

|----|-----|---|----------|--------------------------------------------|

## Halbleiter-Dioden

|    |       |   |                   |                                 |

|----|-------|---|-------------------|---------------------------------|

| 25 | VD4-8 | 5 | SAY 12<br>L2/4    | 1378122105 012321<br>TGL 25 184 |

| 26 | VD1-3 | 3 | SAY 17<br>L2/4    | 1378122105 017288<br>TGL 25 184 |

| 27 | VD9   | 1 | SZK21/5,1<br>L2/4 | 1378122105 017288<br>TGL 27 338 |

| Lfd.<br>Nr.                       | Pos.<br>Kr.   | Stck. | Benennung                                | Sach-Nr.                        |

|-----------------------------------|---------------|-------|------------------------------------------|---------------------------------|

| Schwingquarz                      |               |       |                                          |                                 |

| 20                                | Q1            | 1     | HQ 02<br>16000 kHz                       | 13776117... ....*<br>TGL 43 330 |

| Stromteiler                       |               |       |                                          |                                 |

| 29                                | RH1, RM2      | 2     | Typ 3894<br>8*0,91kOhm<br>4538.8-9446.75 | 1378727701 633940<br>TGL .. ... |