Ingenieurhochschule fuer Seefahrt

Warnemuende/Wustrow

Abteilung Rechentechnik und

wissenschaftlicher Gerätebau

Leiter: Prof. Dr. sc. techn. H. Mennenga

N A N O S

256 kByte DRAM

Entwicklung:

E. Kuecklich

H. Mennenga

Warnemuende, den 29. 09. 1987

Inhaltsverzeichnis

|                                                                 | Seite |

|-----------------------------------------------------------------|-------|

| 1. Einleitung                                                   | 3     |

| 2. Technische Daten                                             | 4     |

| 3. Funktionsbeschreibung                                        | 5     |

| 3.1 Betriebsarten                                               | 5     |

| 3.1.1 Betriebsart RAM-Floppy                                    | 5     |

| 3.1.2 Multiprogrammbetrieb                                      | 6     |

| 3.1.3 Einstellen der Varianten in der Betriebsart<br>RAM-Floppy | 7     |

| 3.1.4 Erzeugung des Signals /MEMDI                              | 7     |

| 3.2 Wirkungsweise der Schaltung                                 | 8     |

| 3.3 Schaltungsbeschreibung                                      | 9     |

| 3.3.1 Speichermatrix                                            | 9     |

| 3.3.2 Die Steuerschaltung                                       | 10    |

| 3.3.3 Generierung der Signale /RAS und /CAS                     | 11    |

| 3.3.4 Der Steuerport                                            | 11    |

| 4. Betrieb der Baugruppe                                        | 12    |

| 4.1 Einstellen der Steuerportadresse (PROM D 9)                 | 12    |

| 4.2 Einstellen des Fensterbereiches (PROM D 8)                  | 14    |

| 4.3 Einstellen des /RAS-Dekodlers (PROM D 4)                    | 16    |

| 4.4 Initialisieren und Steuern der Baugruppe                    | 18    |

| 5. Inbetriebnahme und Pruefung                                  | 20    |

| 5.1 Vorpruefung der unbestueckten Leiterplatte                  | 20    |

| 5.2 Pruefung der bestueckten Leiterplatte                       | 20    |

| 5.2.1 Kontrolle der bestueckten Leiterplatte                    | 20    |

| 5.2.2 Elektrische Kontrolle                                     | 21    |

| 5.2.2.1 Stromaufnahme der Baugruppe                             | 21    |

| 5.2.2.2 Pruefung der Speichergrundfunktionen                    | 21    |

| 5.2.2.3 Dynamischer Speichertest                                | 22    |

| 6. Konstruktive Unterlagen                                      |       |

| - Stromlaufplan                                                 |       |

| - Bestueckungsplan                                              |       |

| - Schalteilliste                                                |       |

| - Leiterbilder                                                  | 24    |

## 1. Einleitung

Diese Baugruppe im Format 95 mm x 170 mm mit K-1520-Systembus, bestueckt mit 32 Bausteinen U 2164, bietet mehrere Betriebsarten. In der Vorzugsvariante bildet sie sowohl den 64-k-Hauptspeicherbereich als auch einen segmentierten Zusatzspeicher von 192 kByte, der ueber ein Fenster im Hauptspeicherbereich erreicht werden kann. Lage und Groesse des Fensters sind programmierbar.

Die Speicherbaugruppe ist weiter in vier 64-k-Byte-Bereiche aufteilbar, die einen gemeinsamen physischen Speicherabschnitt besitzen. Weiter ist es moeglich, bis zu vier derartige Speicher in einem System zu verwenden, wovon eine den Hauptspeicherbereich und den ersten Teil des Zusatzspeichers bildet, die anderen die Erweiterungen des Zusatzspeichers.

Der Einsatz der Baugruppe erfolgt in kassettenorientierten Mikrorechnersystemen (z.B. MC 80) als RAM-Floppy, in Terminals, die ueber ein LAN auf einen gemeinsamen nichtfluechtigen Speicher zugreifen koennen, in Echtzeitrechnern mit Multiprogrammbetrieb usw. Die Baugruppe ist in ein CP/M-kompatibles Betriebssystem eingebunden. Sie ist ein Modul des NANOS-Baugruppensystems, das fuer den wissenschaftlichen Geraeetebau, den Bau von Lehrmitteln und den Ratiomittelbau geschaffen wurde.

## 2. Technische Daten

|                                                |                                                                                                                                                                                                  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - Abmessungen                                  | 95 mm x 170 mm                                                                                                                                                                                   |

| - Elektrischer und mechanischer Anschluss      | K-1520-Systembus nach TGL 37271                                                                                                                                                                  |

| - Betriebsspannung                             | + 5 V                                                                                                                                                                                            |

| - Stromaufnahme                                | ca. 700 mA                                                                                                                                                                                       |

| - Speicherkapazität                            | 256 kByte                                                                                                                                                                                        |

| - Speicherbausteine                            | 256 kDRAM U 2164 oder K 565 RU 5                                                                                                                                                                 |

| - Aufrischzyklen                               | Refresh-Signal und -adressen vom Systembus                                                                                                                                                       |

| - Funktionsprinzip                             | Umsetzung logischer in physische Adressen mittels Fenstertechnik                                                                                                                                 |

| - Betriebsarten                                | <p>1) RAM-Floppy</p> <p>Variante 1: ohne zusätzlichen Arbeitsspeicher</p> <p>Variante 2: mit zusätzlichen Arbeitsspeicher</p> <p>2) Multiprogrammbetrieb</p>                                     |

| - Breite des Fensters bzw. des Commonbereiches | 256 Byte                                                                                                                                                                                         |

| - Steuerung der Baugruppe                      | Über 6 Portadressen mit den Funktionen:                                                                                                                                                          |

|                                                | <p>"Speicher ein"<br/>         "Speicher aus"<br/>         "Lesen freigegeben"<br/>         "Lesen gesperrt"<br/>         "High-Teil der Zieladresse laden"<br/>         "Bank-Nummer laden"</p> |

### 3. Funktionsbeschreibung

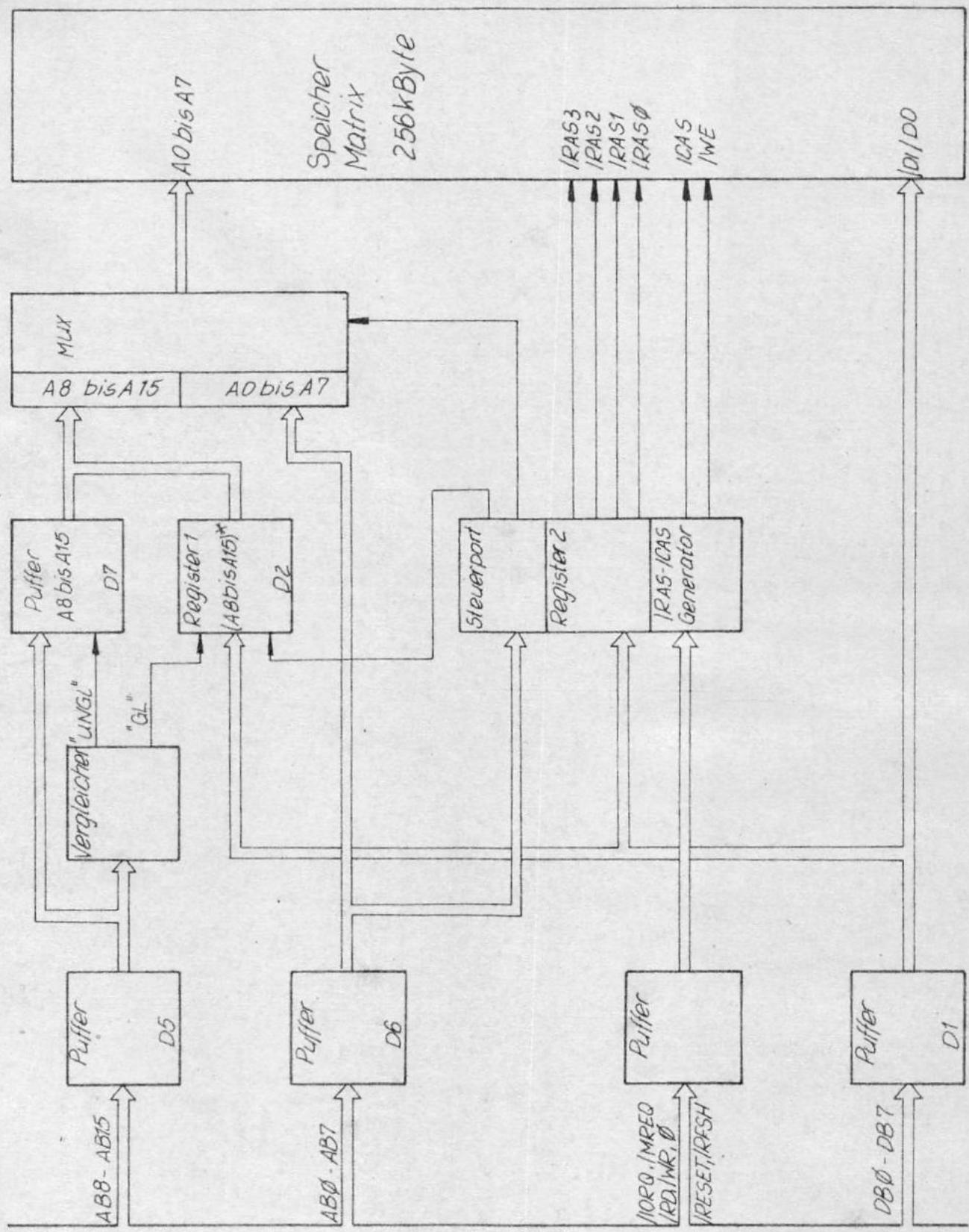

Anhand der Bilder 1 und 2 wird die Funktion der Baugruppe beschrieben. Die vom Rechner ausgegebene Adresse hat eine Breite von 16 Bit, umfasst also einen Speicherraum von 64 kByte (Bild 1.a). Zur Verwaltung aller 256 k Speicherplätze wird die logische Adresse um 2 Bit ergänzt (Bild 1.b). Damit ergibt sich die erforderliche physische Adressbreite von 18 Bit. Die beiden zusätzlichen Bit entscheiden darüber, auf welche der vier 64-k-Banken zugegriffen werden soll. Sie werden mittels Ausgabeoperation in das Register 2 (Bild 2) eingetragen.

Dabei wird unterschieden, ob ein Speicherzugriff innerhalb oder außerhalb des sogenannten Fensterbereiches stattfinden soll (siehe übernächster Absatz). Im ersten Fall werden die Ergänzungsbits mit B0 und B1, im zweiten Fall mit b0 und b1 bezeichnet.

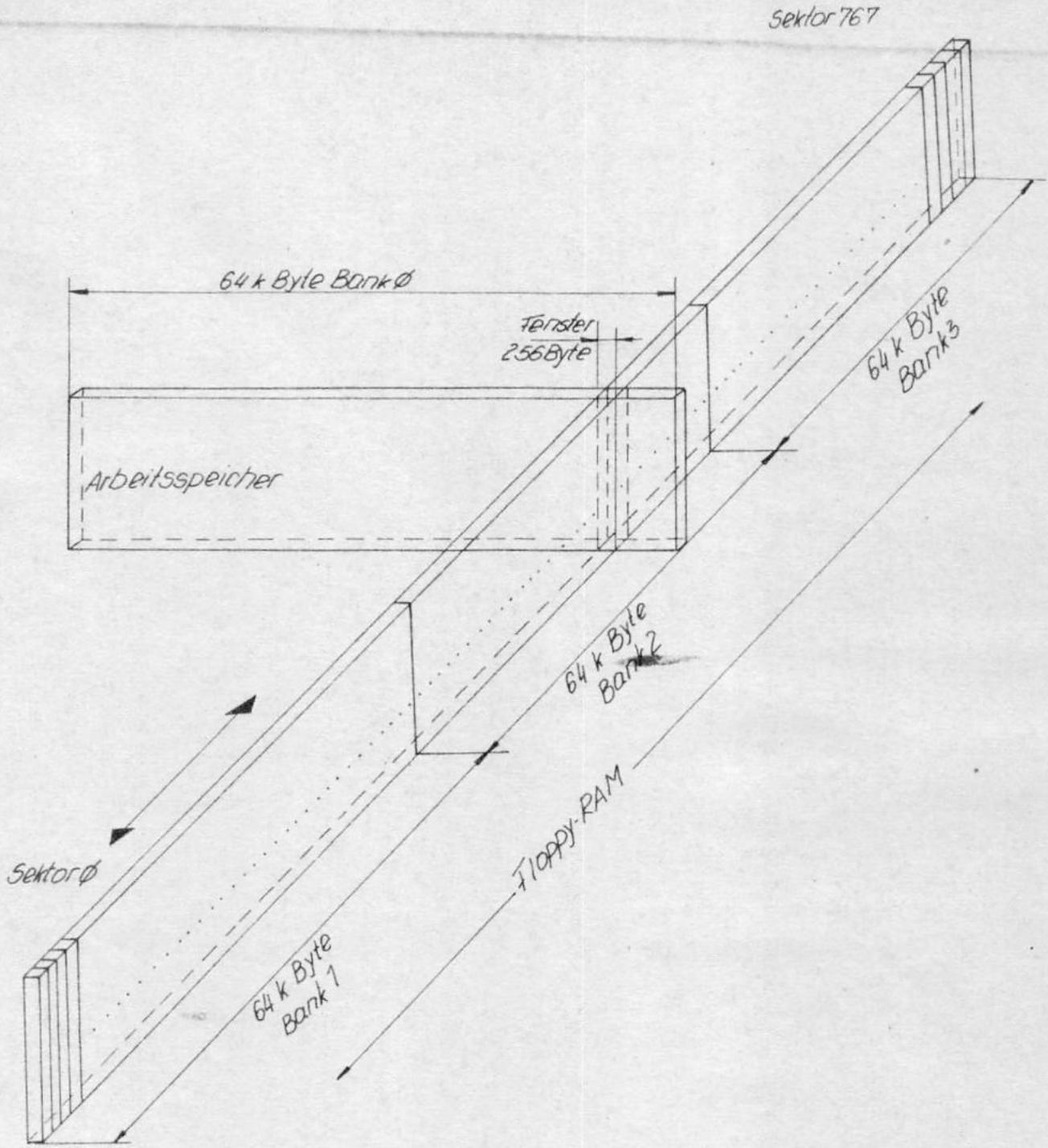

Weiterhin besteht die Möglichkeit, den höherwertigen Teil der logischen Adresse, also die Adressbits A8 bis A15 zu ersetzen durch die in Register 1 gespeicherten Bits A8" bis A15". Damit kann innerhalb der ausgewählten Bank auf einen beliebigen 256-Byte-Block zugegriffen werden.

Die Entscheidung, ob ein Austausch der Bits A8 bis A15 vorgenommen wird oder nicht, hängt davon ab, ob die aktuelle logische Adresse außerhalb oder innerhalb eines vorzugebenden Adressbereiches liegt, der im folgenden als Fensterbereich bezeichnet wird. Liegt die Adresse außerhalb dieses Bereiches, so werden alle 16 Bit unverändert übernommen. Liegt sie dagegen im Fensterbereich, so werden die Bit A8 bis A15 ersetzt durch die Bits A8" bis A15", die vorher in das Register 1 einzutragen sind.

Mit der Ergänzung um zwei Bit und der Substitution der Bits A8 bis A15 (Bild 1,b) bestehen also zwei Möglichkeiten, die logische Adresse zu verändern. Aus der Kombination beider Verfahren ergeben sich grundsätzlich zwei Betriebsarten.

#### 3.1 Betriebsarten der Baugruppe

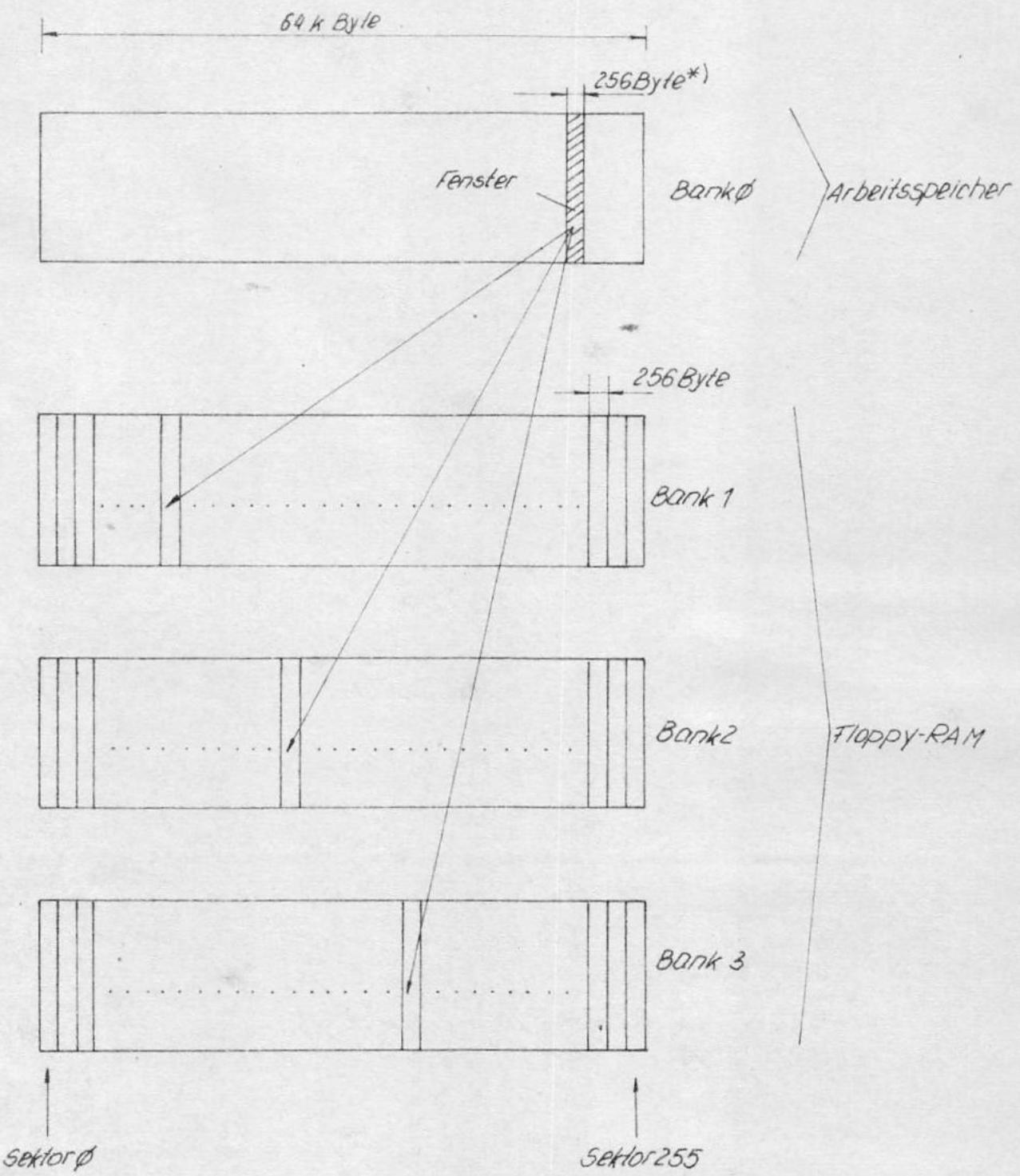

##### 3.1.1 Betriebsart R A M - F l o p p y (Bild 1,c)

In dieser Betriebsart wird eine Bank (vorzugsweise Bank 0) als Arbeitsspeicher des Rechnersystems genutzt. Das bedeutet, dass die logischen Adressen identisch sind mit den physischen Adressen dieser Bank (Bild 1,c1). Ausgenommen davon ist nur der Fensterbereich. Bei einem Zugriff auf diesen Bereich werden sowohl die Adressbits A8 bis A15 als auch die Ergänzungsbits verändert und ergeben die in Bild 1,c2 dargestellte physische Adresse.

Die Betriebsart RAM-Floppy kann in zwei Varianten realisiert werden:

In Variante 1 bildet die Baugruppe sowohl den 64-k-Hauptspeicher als auch den RAM-Floppy. Ein zusätzlicher Arbeitsspeicher ist in solchen Systemen nicht erforderlich. Die Kapazität des Floppy-RAM beträgt in diesem Falle 192 kByte. Diese Betriebsart gestattet den Aufbau besonders einfacher und kleiner Mikrorechnersysteme, bei denen eine Verringerung des Floppy-RAM's um 64 kByte ohne Bedeutung ist. Der Datenaustausch zwischen Hauptspeicher und Floppy-

RAM findet einfach dadurch statt, dass Adressen innerhalb des Fensterbereiches angesprochen werden. Der zugehörige Speicherzugriff erreicht dann denjenigen Sektor im Floppy-RAM, dessen Bank- und Sektornummer vorher an die Baugruppe ausgegeben wurde.

In Variante 2 ist bereits ein Arbeitsspeicher im System vorhanden. Die Baugruppe 256-k-DRAM steht mit ihrer vollen Kapazität als RAM-Floppy zur Verfügung. Sie ist dabei nur für die Adressen innerhalb des Fensters aktiv. Diese Variante kommt zum Einsatz in Systemen, die bereits einen Arbeitsspeicher enthalten und mit einem RAM-Floppy nachgerüstet werden sollen.

Der Datenaustausch zwischen Hauptspeicher und Floppy-RAM wird - programmgesteuert - wie folgt abgewickelt:

- Im Arbeitsspeicher wird der Adressbereich des Fensters physisch abgeschaltet. Die Möglichkeit dazu muss in der betreffenden Baugruppe vorgesehen sein.

- Der Floppy-RAM wird aktiviert. Wird jetzt vom Rechner eine Adresse innerhalb des Fensterbereiches angesprochen, so wirkt der entsprechende Speicherzugriff nicht auf den Hauptspeicher sondern auf den Floppy-RAM. Die Information darüber, welcher Sektor im Floppy-RAM erreicht werden soll, muss vorher an die Baugruppe ausgegeben werden.

- Nach dem Datentransfer wird der Floppy-RAM abgeschaltet und der Fensterbereich im Hauptspeicher wieder aktiviert.

In einer abgerüsteten Variante kann die Baugruppe auch als 64-k-Arbeitsspeicher in Mikrorechnersystemen eingesetzt werden. In diesem Falle werden nur acht Speicherbausteine bestückt. Die Bausteine D 2,3,5 und 8 entfallen.

### 3.1.2 Multiprogramm-Betrieb (Bild 1d)

In dieser Betriebsart wird die Unterscheidung zweier logischer Adressbereiche benutzt, um einem sogenannten Common-Bereich eine unterschiedliche Speicherumgebung zuzuordnen. Der Common-Bereich entspricht physisch dem Fensterbereich in der Betriebsart RAM-Floppy. Er ist in allen vier Speicherbänken in gleicher Weise angelegt; die Ergänzungsbits B0 und B1 sind also konstant. Bei Änderung der Ergänzungsbits b0 und b1 findet für alle logischen Adressen außerhalb des Common-Bereiches eine Umschaltung der Speicherbank statt. Der Common-Bereich selbst bleibt physisch erhalten, wird aber in eine andere logische Umgebung versetzt.

### 3.1.3 Einstellen der Varianten in Betriebsart RAM-Floppy

Die Varianten unterscheiden sich im Wesentlichen dadurch, dass die Baugruppe entweder den 64-k-Hauptspeicher plus 192-k-RAM-Floppy (Variante 1) oder ausschliesslich einen RAM-Floppy von 256 kByte bildet (Variante 2).

In Variante 1 ist die Baugruppe im g e s a m t e n logischen Adressbereich von 64 kByte aktiv. Zugriffe auf das "Fenster" werden in den Floppy-RAM geleitet.

In Variante 2 ist die Baugruppe nur im F e n s t e r aktiv. Alle Zugriffe der CPU auf Adressen ausserhalb des Fensters gelangen zu dem im System angelegten Hauptspeicher.

Zur Einstellung der Variante 1 oder 2 dient die Wickelverbindung X2:1 - X2:2:

|                             |              |

|-----------------------------|--------------|

| X2:1 - X2:2 nicht gewickelt | = Variante 1 |

| X2:1 - X2:2 gewickelt       | = Variante 2 |

Ist diese Verbindung hergestellt, so gelangt das Signal "G1" von DB, Pin 11 an das Gatter D10, Pin 12. Damit kann der /CAS-Impuls und somit ein Speicherzugriff nur fuer "G1" = H, also innerhalb des Fensters erzeugt werden. Ausserhalb des Fensters ist "G1" = T. An D15, Pin 6 kann kein /CAS-Signal entstehen. Damit ist ein Speicherzugriff nicht moeglich. Das Auffrischen des g e s a m t e n Speichers ist aber in jedem Falle sichergestellt.

### 3.1.4 Erzeugung des Signales "/MEMDI"

Wie aus dem Stromlaufplan ersichtlich, gilt fuer die /MEMDI-Generierung folgende Regel: /MEMDI wird erzeugt, wenn die Baugruppe aktiv ist (D14, Pin 9 fuehrt H-Potential) und wenn sie fuer Lesen freigegeben ist (D14, Pin 5 fuehrt H-Potential). Das bedeutet zum Beispiel: Wird die Baugruppe nach RESET oder nach dem Einschalten des Rechners fuer Schreiben freigegeben (Ausgabe an den Port 75H), zum Lesen aber noch nicht zugelassen (D14, Pin 5 verbleibt an T), so wird kein /MEMDI-Signal erzeugt. Das heisst in Variante 2, dass der Hauptspeicher im Bereich des Fensters mit beschrieben wird. Sollte dies nicht zulaessig sein, so muss der Hauptspeicher in diesem Adressbereich fuer die Dauer der Fensterzugriffe gesperrt werden.

### 3.2 Wirkungsweise der Schaltung

Die Wirkungsweise der Schaltung in der Betriebsart 1 wird anhand von Bild 2 und 3 erklärt:

Bild 3 stellt den gesamten Speicher von 256 kByte dar. Er besteht physisch aus 4 Speicherbaenken zu je 64 kByte und bildet daraus sowohl den 64-k-Byte-Hauptspeicher als auch den 192 kByte umfassenden Zusatzspeicher, den eigentlichen Floppy-RAM. Weitere RAM-Baugruppen werden im System nicht besetzt.

Die physischen Adressen der Bank 0 bilden, mit Ausnahme des Fensterbereiches (schraffiert), die logischen Adressen des Rechners. Der Adressraum der Speicherbaenke 1,2 und 3 ist unterteilt in 768 Sektoren zu je 256 Bytes. Das Fenster hat ebenfalls eine Breite von 256 Bytes. Als Basisadresse des Fensterbereiches koennen alle 256 ganzzahligen Moeglichkeiten des logischen Adressraumes genutzt werden: 0000H, 0100H, 0200H,...FE00H und FF00H. Im Baustein D 8 (PROM MH 74S287) wird die Basisadresse des gewählten Fensters niedergelegt (Bild 2). Der Baustein ueberwacht staendig die oberen 8 Bit der vom Rechner gesendeten Adresse. Wenn diese Adresse mit der Fensterbasisadresse uebereinstimmt, wird sie ersetzt durch eine 8-Bit-Adresse, die im Register D 2 (DS 8282) zur Verfuegung steht und vorher mit einem Ausgabebefehl in dieses Register eingetragen werden muss. Ausserdem wird in das Register D 3 (DS 8282) die Information ueber die Speicherbank eingetragen, auf die der naechste Rechnerzugriff erfolgen soll; außerhalb des Fensterbereiches liefert D 3 die Information "Bank 0". Somit ist es moeglich, auf jeden der 768 Sektoren des Floppy-RAM (Bank 1, 2 und 3) zuzugreifen. Die geschilderte Funktion der Baugruppe bewirkt, dass in freier Auswahl jeder Sektor des Floppy-RAM in das Fenster geschoben werden und damit vom Hauptspeicher aus erreicht werden kann (Bild 4).

### 3.3 Schaltungsbeschreibung

Die Schaltung der Baugruppe ist so ausgelegt, dass sie die Arbeit in den unter 3.1 genannten beiden Betriebsarten gewährleistet. Sie enthält die folgenden Funktionsgruppen:

- Speichermatrix

- Adressenmultiplexer

- Generierung der RAS- und CAS-Impulse sowie der Steuersignale für den Multiplexer

- Steuerung der Funktionen "Speicher aktiv/inaktiv" und "Lesen gesperrt/freigegeben"

- Ausgabeport und Register zur Übergabe der Steuersignale und Sektoradressen an die Baugruppe

- Adressenvergleicher zur Erkennung des Fensterbereiches

- Pufferung für alle Bussignale nach TGL 37271.

#### 3.3.1 Speichermatrix

Die Speichermatrix (Stromlaufplan Blatt 2) enthält die 32 Speicherbausteine vom Typ U 2164 (DRAM 64k x 1 Bit). Je 8 Stück bilden eine Speicherbank von 64 kByte, so dass insgesamt 256 kByte Speicherkapazität zur Verfügung stehen. Dateneingang und Datenausgang eines Speicherbausteins sind miteinander verbunden. Diese Schaltungsvariante ist zulässig, wenn bei Schreiboperationen das Schreibsignal des Bausteins (/WE) vor dem /CAS-Impuls aktiv wird, da in diesem Fall der Ausgang im hochohmigen Zustand verbleibt.

Jeder Speicherbaustein besitzt somit nach aussen nur eine Datenleitung. Die Datenleitungen gleicher Wertigkeit, also jeweils vier, sind miteinander verbunden, so dass die Speichermatrix über acht bidirektionale Datenleitungen mit dem Datentreiber D 1 (DS 8286) verbunden ist.

Die gleichwertigen Adressenanschlüsse aller Speicher-IC sind ebenfalls miteinander verbunden. Das gleiche gilt für die WE- und CAS-Anschlüsse.

Die Auswahl der Speicherbank geschieht mit dem RAS-Signal. Dazu sind die RAS-Anschlüsse jeweils einer Speicherbank miteinander verbunden. Die Bankauswahl mittels RAS-Signal wurde gewählt, um die Stromaufnahme der Matrix und damit der Baugruppe zu minimieren.

Die Speichermatrix besitzt also nach aussen die folgenden Anschlüsse:

- 8 Datenleitungen (D0 bis D7, bidirektional)

- 8 Adressleitungen (A0 bis A7)

- 4 Bankselektsignale (/RAS0 bis /RAS3)

- 1 /CAS-Signal

- 1 /WE-Signal.

Das periodische Auffrischen der Speicherinhalte geschieht

durch Aufschalten des RAS-Signales an alle 32 Speicherbausteine (RAS-only-refresh) bei gleichzeitigem Anlegen der aktuellen Refresh-Adresse. Hierzu werden die vom Prozessor U 880 gelieferten Signale benutzt.

### 3.3.2 Die Steuerschaltung

Die Steuerschaltung vermittelt den Informationsaustausch zwischen dem Bus des Rechnersystems und der Speichermatrix. Am Beispiel der Betriebssäge 1 wird die Wirkungsweise geschildert (siehe Stromlaufplan und Bild 2).

Die vom Rechner ausgesandte Adresse gelangt an die beiden Adresspuffer D 5 und D 6 (8282). Die 16-Bit-Adresse des Rechners wird in zwei Schritten zu je 8 Bit mit den Signalen /RAS und /CAS in die Speichermatrix übernommen. Der dafür erforderliche Multiplexer besteht aus den Schaltkreisen D 6, D 7, D 3 und D 2, die wie folgt gesteuert werden:

Die niedrigwertigen 8 Bit der Adresse werden über den Adresspuffer D 6 zum Zeitpunkt der H/T-Flanke des /RAS-Impulses in die ausgewählte Speicherbank übernommen. D 6 wird mit Beginn des /CAS-Impulses abgeschaltet.

Die höherwertigen 8 Bit der Adresse liegen ständig am Vergleicher D 9 an, der darüber entscheidet, ob die bevorstehende Speicheroperation außerhalb oder innerhalb des Fensterbereiches stattfindet. Im ersten Falle wird der Ausgang "UNGL" des Vergleichers aktiv. Dies bewirkt, dass über D 7 die höherwertigen Addressbits des Rechners unverändert zur Speichermatrix durchgeschaltet und mit der H/T-Flanke des /CAS-Impulses übernommen werden. Im Decoder (D 4) wird – in der Vorzugsvariante – das Bankauswahlsignal RAS 0 erzeugt (da b0 = b1 = 0).

Im zweiten Fall – Adresse fällt in den Fensterbereich – wird der Ausgang "GL" des Vergleichers aktiv. Damit bleibt D 7 gesperrt und die höherwertigen 8 Bit der logischen Adresse gelangen nicht zur Speichermatrix. Sie werden substituiert durch die im Register D 2 enthaltenen 8 Bit der Zieladresse für den Floppy-RAM. Register D 3 enthält die Information über die Speicherbank, in der diese Adresse angesprochen werden soll. Im Decoder D 4 wird das dazu erforderliche Auswahlsignal /RAS 1, /RAS 2 oder /RAS 3 erzeugt. Die Information über die gewünschte Zieladresse muss vorher durch Ausgabeoperationen an den Steuerport der Baugruppe in den Registern D 2 und D 3 abgelegt werden.

### 3.3.3 Generierung der Signale /RAS und /CAS

Der Speicherbaustein U 2164 (Äquivalent: K 565 RU 5) übernimmt seine 16-Bit-Adresse in zwei Schritten zu je 8 Bit. Dies geschieht nacheinander mit den Signalen /RAS und /CAS. Das /RAS-Signal ist abgeleitet aus dem /MREQ-Impuls der CPU. /MREQ gelangt über zwei Gatter der IS 11 an den /RAS-Decoder D 4 (PROM MH74 S287). In diesem Baustein wird bereits mit Ausgabe der CPU-Adressen über die Signale "GL" und "UNGL" und durch Verknüpfung mit den Bankauswahlsignalen b0, b1, B0 und B1 das für die bevorstehende Speicheroperation erforderliche /RAS-Signal vorbereitet und zum Zeitpunkt der H/T-Flanke des /MREQ-Impulses zur ausgewählten Speicherbank durchgeschaltet. Zu diesem Zeitpunkt liegen an den Adresseingängen der Speichermatrix die Adressbits 0 bis 7 an, da der Puffer D 6 wegen T-Potential an 6"13 eingeschaltet ist. Einen halben Takt später wird IS 13 umgeschaltet. D 6 wird gesperrt. An die Eingänge 2"15 und 12"15 gelangt H-Potential. Je nachdem, ob die ablaufende Speicheroperation außerhalb oder innerhalb des Fensterbereiches stattfinden soll, werden mit dem Signal "UNGL" die Originaladressen über D 7 oder mit dem Signal "GL" die substituierten Adressen aus Register D 2 durchgeschaltet. Wegen der Laufzeiten der Adressen durch D 7 bzw. D 2 muss der /CAS-Impuls geringfügig verzögert werden, da er nicht vor Anliegen stabiler Adressen an der Speichermatrix eintreffen darf. Diese Verzögerung wird mit C1 eingestellt. Sie beträgt ca. 60 ns.

In der Stellung "Speicher aus" wird der /CAS-Impuls wegen T-Potential an 5"15 gesperrt. Damit sind Schreiber- oder Leseoperationen im Speicher nicht möglich.

Das regelmäßige Aufrischen der Speicherinhalte ist auch bei "Speicher aus" gewährleistet. Das /RFSH-Signal des Rechners ist negiert mit dem höchstwertigen Adressbit des PROM's D 4 (/RAS-Decoder) verbunden (15"4). D 4 ist so programmiert, dass die Adressen 80H bis OFFH auf allen 4 Bit den Wert "0" enthalten. Damit werden bei aktivem Refresh-Signal auf allen vier Speicherbauden die erforderlichen /RAS-Signale erzeugt ("/RAS-only-refresh"). Gleichzeitig wird wegen T-Potential an 1"10 der Takt an 3"13 gesperrt, Flipflop D 13 verbleibt in der Ausgangsstellung, und mit T-Potential an 9"6 werden die aktuellen Refresh-Adressen (AB 0 bis AB 7) zur Speichermatrix durchgeschaltet.

Im Anhang sind in Impulsdigrammen die zeitlichen Abläufe für die Operationen.

- Befehlsholezyklus (M1-Zyklus),

- Speicher Schreiben und Lesen und

- Port Schreiben

auf der Baugruppe ausführlich dargestellt.

### 3.3.4 Der Steuerport

Die Arbeitsweise der Baugruppe 256-k-DRAM wird durch sechs Einzelfunktionen gesteuert:

- a) "Speicher ein"

- b) "Speicher aus"

- c) "Lesen freigegeben"

- d) "Lesen gesperrt"

- e) "Ausgabe Banknummer"

- d) "Ausgabe Sektornummer".

Nach RESET oder Einschalten des Rechners sind automatisch die Funktionen "Speicher aus" und "Lesen gesperrt" eingestellt. Bei "Speicher aus" ist zwangsweise "Lesen gesperrt" gegeben. Erfolgt die Freigabe des Speichers ("Speicher ein"), so kann der gesamte Speicher beschrieben, jedoch noch nicht gelesen werden. Das Lesen wird erst nach Ausgabe der Steuerfunktion "Lesen freigegeben" möglich.

Alle sechs Steuerfunktionen werden durch A u s g a b e - Operationen an frei wählbare Portadressen realisiert. Die Verknüpfung der Adressbits AB 0 bis AB 7 mit den Signalen /IORQ und /WR geschieht im D 9 (PROM MH 74 S287). D 9 ist entsprechend den gewählten Portadressen zu programmieren. Die Funktionen "Speicher ein/aus" und "Lesen freig./gesp." werden im D-Flipflop D 14 (DL 074) gespeichert. Das Adressbit 0 wird nicht unmittelbar zur Adressdekodierung herangezogen; es liegt am D-Eingang des Flipflop D 14 und entscheidet, ob die Funktionen "Speicher ein" bzw. "Lesen erlaubt" oder "Speicher aus" bzw. "Lesen gesperrt" eingestellt werden. Für den ersten Fall muss AB 0 = 1, für den zweiten Fall AB 0 = 0 gewählt werden.

Die Programmierung des PROMS für den Steuerport wird unter 4.1 beschrieben. Die Baugruppe belegt 8 I/O-Adressen.

#### 4. Betrieb der Baugruppe

Wichtige logische Verknüpfungen auf der Baugruppe wie

- die Dekodierung der Portadressen,

- die Erkennung des Fensterbereiches und

- die /RAS-Dekodierung

werden mit Hilfe von PROM's ausgeführt. Ein PROM ersetzt dabei mindestens zwei übliche TTL-Schaltkreise. Eine Realisierung der Speicherkapazität von 256 kByte und aller erforderlichen Steuerfunktionen auf einer Karte von 95 mm x 170 mm wäre sonst nicht möglich gewesen.

Um dem Anwender die Möglichkeit zu geben, die Baugruppe den unterschiedlichen Betriebsbedingungen anzupassen, werden die drei PROMS D 4, D 8 und D 9 auf Fassungen gesteckt.

Eine weitere Fassung ist vorgesehen für den Steuerflipflop D 14. In der Inbetriebnahme und Testphase wird dieser Baustein noch nicht eingesteckt. Damit wird eine einfache Prüfung der Grundfunktionen des Speichers möglich.

##### 4.1 Einstellen der Steuerportadressen (PROM D 9)

Der Baustein verknüpft die Adressen AB 1 bis AB 7 mit den Rechnersignalen /IORQ und /WR. Da die Steuereingänge V1 und V2 des Bausteins ebenfalls zur Verknüpfung benutzt werden, führen alle Ausgänge (Y1 bis Y4) im inaktiven Zustand H-Potential. Die Steuersignale am Ausgang des Bausteins sind

steht Taktiv. Die an den Steuereingängen liegenden Signale /IORQ und /WR werden im I/OZyklus erst nach den Adressen aktiv. Sie taktten damit den Baustein IS 9, so dass Stoerspitzen an den Ausgängen, die beim Adressenwechsel auftreten können, vermieden werden. Wird eine ausgegebene Adresse erkannt, so nimmt der betreffende Ausgang T-Potential an. Die vier Ausgänge Y1 bis Y4 steuern folgende Funktionen der Baugruppe:

- Y1: Die Adressbits AB" bis A15" werden in das Register D 2 geladen.

PROM-Inhalt: 1 1 1 0 B = E0 H

- Y2: Die dualen Bankauswahlsignale b0, b1, B0 und B1 werden in das Register D 3 geladen.

PROM-Inhalt: 1 1 0 1 B = D0 H

- Y3: Das Steuerflipflop für die Speicheraktivierung (D 14/1) wird gesetzt oder rückgesetzt in Abhängigkeit von Adressbit 0.

PROM-Inhalt: 1 0 1 1 B = B0 H

- Y4: Das Steuerflipflop für die Lesefreigabe (D 14/2) wird gesetzt oder rückgesetzt in Abhängigkeit von Adressbit 0.

PROM-Inhalt: 0 1 1 1 B = 07 H

Ist AB0 = 0, so wird das betreffende Flipflop zurückgesetzt ("Speicher aus" bzw. "Lesen gesperrt").

Ist AB0 = 1, so wird das betreffende Flipflop gesetzt ("Speicher ein" bzw. "Lesen freigegeben").

Damit können die genannten Funktionen ohne vorheriges Laden eines Ausgaberegisters eingestellt werden.

Im Interesse einer einfachen Leiterführung wurde beim Layout-Entwurf darauf verzichtet, die Adresseingänge des PROM's ihrer Wertigkeit gemäß mit den Bus-Adressleitungen zu verbinden. Die logischen Adressen auf dem Bus stimmen deshalb nicht mit den im PROM programmierten Adressen überein. Die Zuordnung wird im Folgenden angegeben und ist beim Programmieren zu beachten:

Adressbus: AB7 AB6 AB5 AB4 AB3 AB2 AB1 AB0

PROM-Adr.: A6 A5 A4 A3 A0 A1 A2 XX

(A7 des PROMS ist mit MP verbunden!)

**B e i s p i e l :** Die Funktionen der Baugruppe sollen über die folgenden Portadressen gesteuert werden:

- 70 H: HIGH-Teil der Adresse laden ("LDAH")

- 72 H: Bankauswahlsignale b0, b1, B0, B1 laden ("LDBB")

- 74 H: "Speicher aus" ("RAMDI")

- 75 H: "Speicher ein" ("RAMEN")

- 76 H: "Lesen gesperrt" ("READDI")

- 77 H: "Lesen freigegeben" ("READEN")

Die Portadresse

0 1 1 1 0 0 0 0 B = 70 H

wird aufgrund der oben angegebenen Zuordnung im PROM zu

256 kByte DRAM/- 14 -

0 0 1 1 1 0 0 0 B = 38 H.

Die Portadresse

0 1 1 1 0 0 1 0 B = 72 H

wird zu

0 0 1 1 1 1 0 0 B = 3C H.

Insgesamt ergibt sich fuer die gewahlten Portadressen das folgende Schema:

| Portadresse | PROM-Adresse | PROM-Inhalt |          |

|-------------|--------------|-------------|----------|

|             |              | binaer      | hexadez. |

| 70 H        | 38 H         | 1 1 1 0     | 0E       |

| 72 H        | 3C H         | 1 1 0 1     | 0D       |

| 74 H        | 3A H         | 1 0 1 1     | 0B       |

| 75 H        | 3A H         | 1 0 1 1     | 0B       |

| 76 H        | 3E H         | 0 1 1 1     | 07       |

| 77 H        | 3E H         | 0 1 1 1     | 07.      |

#### 4.2 Einstellen des Fensterbereiches (PROM D 8)

Der PROM D 8 vergleicht die oberen acht Bit der vom Rechner gesendeten 16-Bit-Adresse mit der gewahlten Fensterbasisadresse. Stimmen beide ueberein, so erfolgt ein Speicherzugriff auf den RAM-Floppy. Da der Adressraum des Rechners 65536 Byte betraegt und die hoherwertigen 8 Adress-Bit davon zum Vergleich herangezogen werden, hat der Fensterbereich eine Breite von 256 Byte. Als "Fensterbasisadresse kann also jeder Wert der Folge

0000 H, 0100 H, 0200 H, ..., FD00 H, FE00 H, FF00 H

gewahlt werden.

Der PROM D 8 muss somit an seinen Ausgaengen Y1 und Y2 folgenden Signale erzeugen:

"UNGL"      "GL"

- Im Fensterbereich:                    Y1 = 0      Y2 = 1

- Ausserhalb des Fensterbereiches:    Y1 = 1      Y2 = 0.

Auch beim Programmieren des PROM's D 8 ist die veraenderte Adressenzuordnung zu beachten:

Adressbus: AB7 AB6 AB5 AB4 AB3 AB2 AB1 AB0

PROM-Adr.: A6 A5 A4 A3 A0 A1 A2 A7

Beispiel: Der Wert der Fensterbasisadresse sei

F 7 0 0 H .

Die Baugruppe arbeitet in Betriebsart 1. Die oberen 8 Bit dieser Adresse lauten :

1 1 1 1 0 1 1 1

Mit der o.a. Zuordnung erhält man folgende Adresse im PROM:

1 1 1 1 1 1 1 0

also den hexadezimalen Wert FE .

Das Programmierschema für den PROM II 8 lautet somit für die gewählte Portadresse und Betriebsart 1:

| PROM-Adresse | PROM-Inhalt |          |

|--------------|-------------|----------|

|              | binder      | hexadez. |

| FE H         | 0 0 1 0     | 02       |

| alle übrigen | 0 0 0 1     | 01 .     |

#### 4.3 Einstellen des /RAS-Dekoders (PROM D 4)

Im Baustein D 4 werden die logischen Verknuepfungen zur Gewinnung der /RAS-Signale ausgefuhrt. Als Eingangsgrössen liegen an:

- die Signale "GL" und "UNGL" vom Adressenvergleicher,

- die Blockauswahlsignale b0, b1, B0 und B1 und

- das Refresh-Signal der CPU.

Entsprechend der in 3.3 beschriebenen Wirkungsweise der Baugruppe dienen die vier /RAS-Signale zur physischen Auswahl der Speicherbaenke. Die logische Verwaltung geschieht so, dass (in der Vorzugsvariante) fuer alle Speicherzugriffe ausserhalb des Fensters physische Adressen der Bank 0 angesprochen werden. Fuer Speicherzugriffe innerhalb des Fensters werden, je nachdem, ob Bank 1, 2 oder 3 erreicht werden soll, die Signale /RAS1, /RAS2 oder /RAS3 erzeugt. Dabei werden die Bankauswahlsignale B0 und B1 aus Register D 3 bewertet, in denen die anzusprechende Speicherbank dual verschluesselt ist.

Während des Refresh-Vorganges muss fuer alle Speicherbaenke gleichzeitig das /RAS-Signal erzeugt werden (/RAS-only-refresh). Das RFSH-Signal der CPU ist an das höchstwertige Adressbit des PROM's angeschlossen. Die Adressen 80 H bis OFF H werden in allen vier Bit mit "0" programmiert, so dass bei /RFSH die Signale /RAS0 ... /RAS3 gleichzeitig erzeugt werden.

Insgesamt liegen der Programmierung des PROM's D 4 die folgenden Verknuepfungen zugrunde:

$$\text{RAS0} = \text{UNGL} * \text{GL} * \text{b0} * \text{b1} + \text{RFSH}$$

$$\text{RAS1} = \text{/UNGL} * \text{GL} * \text{B0} * \text{B1} + \text{RFSH}$$

$$\text{RAS2} = \text{/UNGL} * \text{GL} * \text{/B0} * \text{B1} + \text{RFSH}$$

$$\text{RAS3} = \text{/UNGL} * \text{GL} * \text{B0} * \text{B1} + \text{RFSH}$$

Die 256 Speicherplaetze des PROM's D 4 sind also wie folgt zu programmieren:

- In die Adressen 80 H bis OFF H wird "0" eingetragen (/RFSH-Generierung)

- In die Speicherplaetze 00 H bis 7F H werden die in der folgenden Tabelle angegebenen Inhalte eingetragen:

| Adresse<br>hex. | Inhalt<br>hex. | Adresse<br>hex. | Inhalt<br>hex. | Adresse<br>hex. | Inhalt<br>hex. |

|-----------------|----------------|-----------------|----------------|-----------------|----------------|

| 00              | 0F             | 2C              | 0F             | 58              | 0F             |

| 01              | 0E             | 2D              | 0B             | 59              | 07             |

| 02              | 0E             | 2E              | 0B             | 5A              | 0B             |

| 03              | 0F             | 2F              | 0F             | 5B              | 0F             |

| 04              | 0F             | 30              | 0F             | 5C              | 0F             |

| 05              | 0E             | 31              | 0B             | 5D              | 07             |

| 06              | 0E             | 32              | 0B             | 5E              | 0B             |

| 07              | 0F             | 33              | 0F             | 5F              | 0F             |

| 08              | 0F             | 34              | 0F             | 60              | 0F             |

| 09              | 0B             | 35              | 0B             | 61              | 0E             |

| 0A              | 0E             | 36              | 0F             | 62              | 07             |

| 0B              | 0F             | 37              | 0F             | 63              | 0F             |

| 0C              | 0F             | 38              | 0F             | 64              | 0F             |

| 0D              | 0B             | 39              | 07             | 65              | 0E             |

| 0E              | 0E             | 3A              | 0B             | 66              | 07             |

| 0F              | 0F             | 3B              | 0F             | 67              | 0F             |

| 10              | 0F             | 3C              | 0F             | 68              | 0F             |

| 11              | 0D             | 3D              | 07             | 69              | 0B             |

| 12              | 0E             | 3E              | 0B             | 6A              | 07             |

| 13              | 0F             | 3F              | 0F             | 6B              | 0F             |

| 14              | 0F             | 40              | 0F             | 6C              | 0F             |

| 15              | 0D             | 41              | 0E             | 6D              | 0B             |

| 16              | 0E             | 42              | 0D             | 6E              | 07             |

| 17              | 0F             | 43              | 0F             | 6F              | 0F             |

| 18              | 0F             | 44              | 0F             | 70              | 0F             |

| 19              | 07             | 45              | 0E             | 71              | 0B             |

| 1A              | 0E             | 46              | 0B             | 72              | 07             |

| 1B              | 0F             | 47              | 0F             | 73              | 0F             |

| 1C              | 0F             | 48              | 0F             | 74              | 0F             |

| 1D              | 07             | 49              | 0B             | 75              | 0D             |

| 1E              | 0E             | 4A              | 0D             | 76              | 07             |

| 1F              | 0F             | 4B              | 0F             | 77              | 0F             |

| 20              | 0F             | 4C              | 0F             | 78              | 0F             |

| 21              | 0E             | 4D              | 0B             | 79              | 07             |

| 22              | 0B             | 4E              | 0D             | 7A              | 07             |

| 23              | 0F             | 4F              | 0F             | 7B              | 0F             |

| 24              | 0F             | 50              | 0F             | 7C              | 0F             |

| 25              | 0E             | 51              | 0D             | 7D              | 07             |

| 26              | 0B             | 52              | 0D             | 7E              | 07             |

| 27              | 0F             | 53              | 0F             | 7F              | 0F             |

| 28              | 0F             | 54              | 0F             |                 |                |

| 29              | 0B             | 55              | 0D             |                 |                |

| 2A              | 0B             | 56              | 0D             |                 |                |

| 2B              | 0F             | 57              | 0F             |                 |                |

Tabelle zur Programmierung des PROM's D4

#### 4.4 Initialisieren und Steuern der Baugruppe RAM-Floppy

Nach RESET (auch nach dem Einschalten) befindet sich die Baugruppe im inaktiven Zustand, da 9"14" an T-Potential liegt und kein /CAS-Signal gebildet werden kann.

Gleichzeitig wird auch an 5"14 T-Potential erzeugt, womit das Lesen der Baugruppe nicht möglich ist.

Die für den Datenerhalt im Speicher erforderlichen Auffrischungszyklen werden auch im inaktiven Zustand ausgeführt.

#### Steueraadressen

|                      | Adresse | Inhalt                     | Symbol |

|----------------------|---------|----------------------------|--------|

| "Speicher aus"       | 74 H    | xx                         | RAMDI  |

| "Speicher ein"       | 75 H    | xx                         | RAMEN  |

| "Lesen gesperrt"     | 76 H    | xx                         | READBI |

| "Lesen freigegeben"  | 77 H    | xx                         | READEN |

| "High-Adresse laden" | 70 H    | High-Byte                  | LDAH   |

| "Bank-Nummer laden"  | 72 H    | B0,B1,b0,b1,<br>x, x, x, x | LDBB   |

Füllt eine logische Adresse in das Fenster, d. h. in den Adressbereich von F700 H bis F7FF H, so werden die oberen 8 Adressbits AB15 bis AB8 durch die Adressbits LDAH ersetzt. Die Banksteuerung erfolgt dann über die Signale B0 und B1. Außerhalb des Fensters wird die Bankauswahl über die Bits b0 und b1 vorgenommen, wobei vorzugsweise mit b0 = b1 = 0 die Bank 0 ausgewählt wird.

Die Funktionen RAMDI, RAMEN, READBI und READEN werden in den beiden Flipflop von B14 gespeichert.

Die vorliegende Version der Baugruppe (R 233-101/12.1 vom 12. II. 86) gestattet den Einsatz in beiden Varianten der Betriebsart "RAM-Floppy". Sie kann also als alleinige Speicherbaugruppe in einem Rechnersystem arbeiten als auch neben einem vorhandenen Hauptspeicher eingesetzt werden.

Für den Einsatz als 256-K-RAM-Floppy ist die Brücke X 2:1 nach X 2:2 zu schließen. Damit kann die Baugruppe generell nur im Fenster (bei "GL" = 1) aktiv werden. Die Verknüpfung mit dem Speicheraktivierungssignal RAMEN erfolgt im Datter Di0/4.

Für die Betriebsart "256-K-RAM-Floppy" sind in einem Initialisierungsvorgang folgende Stufen zu durchlaufen:

1. Nach Reset oder dem Einschalten des Systems ist das Signal RAMDI aktiv, d. h. an 11"10 liegt T-Potential. Dies bewirkt:

- Sperrung des /CAS-Impulses an 5"15,

- Richtungssignal des Datenpuffers steht auf "Schreiben"

- und das /MEMDI-Signal an X1:39 auf "H".

Die Baugruppe ist – auch im Fensterbereich – inaktiv. Der logische Adressbereich ist durchgehend identisch mit dem 64-K-Arbeitsspeicher.

2. Das Signal RAMEN wird aktiviert ("H" an 13"10): Für logische Adressen innerhalb des Fensterbereiches entsteht auch an 12"10 und damit an 11"10 H-Potential. Dies be-

wirkt:

- Freigabe des /CAS-Impulses an S'15,

- das Richtungssignal des Datentreibers steht weiterhin auf Schreiben, da S'14 noch an "T" liegt.

- Damit koennen Schreibeoperationen ueber das Fenster auf das RAM-Floppy ausgefuehrt werden.

- Wegen "T" an S'14 wird kein /MEMDI generiert, d. h. die Schreibeoperationen wirken auch auf den Arbeitsspeicher des Systems, sofern der Fensterbereich dort nicht abgeschaltet wurde.

3. Zusätzlich zum Signal RAMEN wird das Signal READEN aktiviert:

Damit wird die Baugruppe auch zum Lesen freigegeben, da

das H-Signal an S14 ueber D12/4 die Umschaltung des Datentreibers ermoeglicht als auch - fuer Lesen und fuer Schreiben - /MEMDI generiert.

Bleibi die Bruecke X 2:1 nach X 2:2 offen, so arbeitet die Baugruppe in der Betriebsart "64-K-Hauptspeicher + 192-K-RAM-Floppy".

## 5. Inbetriebnahme und Pruefung

### 5.1 Vorpruefung der unbestueckten Leiterplatte

#### 5.1.1 Sichtkontrolle auf Kupferbruecken und Unterbrechungen

Diese Kontrolle ist sehr gruendlich durchzufuehren, da erfahrungsgemaess bis zu 95 % aller Fehler bei der Inbetriebnahme auf derartige Maengel zurueckzufuetren sind.

Bei groesseren Stueckzahlen ist zu pruefen, inwieweit Rationalisierungsmittel wie Nadelbeittadapter o. a. eingesetzt werden koennen.

#### 5.1.2 Kontrolle der Isolation zwischen den Stromversorgungsanschluessen

Die Anschluesse XS: A1, B1 - A29, B29

sind z. B. mit Vielfachmesser in der Betriebsart "Widerstandsmessung" auf Isolation zu pruefen.

Die Pruefung auf Kurzschluesse und Unterbrechungen ist besonders auf der Bestueckungsseite von Bedeutung, da Fehler hier nach der Bestueckung nur noch schwer zu finden und zu beseitigen sind.

## 5.2 Pruefung der bestueckten Leiterplatte

### 5.2.1 Kontrolle der bestueckten Leiterplatte

- Die Leiterplatte ist auf korrekte Bestueckung gemaeess Bestueckungsplan zu pruefen. Dabei ist sowohl auf den Bobsteintyp als auch auf seine richtige Lage bezueglich der Anschluesse SP und MP zu achten. Bei Elektrolytkondensatoren ist der richtige Anschluss bezueglich ihrer Polaritaet zu kontrollieren.

- Es ist erneut zu pruefen, ob auf der Loetseite Zinnbruecken entstanden sind, wie sie besonders bei busartigen Leitungsstrukturen auftreten koennen.

## 5.2.2 Elektrische Kontrolle

### 5.2.2.1 Stromaufnahme der Baugruppe

Die Baugruppe wird zunächst nur an die Versorgungsspannung von + 5V angeschlossen. Die PROM's D4, D8 und D9 werden nicht eingesteckt. Die Stromaufnahme muss jetzt etwa 380 mA betragen. Nach dem Einsticken der drei PROM's muss sich die Stromaufnahme auf etwa 550 mA erhöhen.

Die Baugruppe wird jetzt auf einen Testrechner gesteckt und erhält damit Verbindung zum Rechnerbus. Bedingt durch die einsetzenden Refresh-Vorgänge steigt die Stromaufnahme auf ca. 700 mA an und hat damit ihren normalen Betriebswert erreicht:

| Messbedingung                                              | Stromaufnahme |

|------------------------------------------------------------|---------------|

| Baugruppe ohne D4, D8, D9<br>(nur SP und MP angeschlossen) | 380 mA        |

| Baugruppe mit D4, D8, D9<br>(nur SP und MP angeschlossen)  | 550 mA        |

| Baugruppe mit D4, D8, D9<br>(Betrieb am Systembus K 1520)  | 700 mA        |

Beim Betrieb am Rechner ist darauf zu achten, dass ein auf diesem Rechner laufendes Programm (Betriebssystem, Testmonitor o.a.) nicht abstürzt, was auf Buskonflikte, verursacht durch die gesteckte Baugruppe, hinweisen würde. In diesem Falle ist das System sofort abzuschalten.

Zweckmäßig ist daher eine Kontrolle der Eingänge der Baugruppe, bei der nur die Betriebsspannung von + 5V angeschaltet ist. Alle TTL-Eingänge müssen unbestimmtes Potential führen. Weiterhin muss das Steuerflipflop D 14 nach Ansprechen der /RESET-Leitung (T-Potential an A 20) zurückgesetzt werden, d. h. es muss an den Anschlüssen 5 und 9 T-Potential führen.

Der Datentreiber D 1 (DS 8282) muss am DIR-Anschluss PIN 11 H-Potential führen, zeigt also mit Eingängen zum Bus und kann dessen Datenleitungen nicht blockieren.

Die /MEMDI-Leitung muss inaktiv sein (H-Potential an B9).

### 5.2.2.2 Prüfung der Speicher-Grundfunktionen

Die eigentliche Speicherprüfung wird zweckmäßig auf einem Rechnersystem ausgeführt, das sowohl eine einfache Kontrolle einzelner Speicherzyklen der CPU (Schreiben und Lesen in möglichst grossen Adressbereichen) als auch einen dynamischen Speichertest mit Testprogrammen gestattet.

Da man nicht von Anfang an auf die einwandfreie Funktion der Baugruppe als Arbeitsspeicher im System zurückgreifen kann, denn dies würde ja bereits eine fehlerfreie Baugruppe voraussetzen, ist es zweckmäßig, vorerst einen Teil des Adressbereiches des Speichers zu sperren, um in diesem Bereich ein residentes Testsystem unterzubringen.

Dieses Testsystem benötigt in der Regel nicht mehr als ca. 4 kByte. Die verbleibenden 60 kByte werden von Adressen der zu testenden Baugruppe belegt und können auf ihre einwandfreie Funktion geprüft werden. Ist diese Funktion nachgewiesen,

so kann durch Kopieren des residenten Testsystems in das Testobjekt und Abschalten der Festwertspeicher ueber das /MEMDI-Signal des Testobjektes der gesamte Arbeitsspeicher (Bank 0) in die Pruefung einbezogen werden.

Dazu muss zuvor die zu testende Baugruppe im gesamten Speicherbereich aktiviert werden.

Jetzt ist auch der Bereich des Floppy-RAM's (die Speicherbaenke 1, 2 und 3) ueber das Fenster vom Arbeitsspeicher aus zu erreichen und zu testen.

Die erste Kleiasserie von 256kDRAM-Baugruppen wurde auf einem Rechnersystem mit residentem Testmonitor geprueft. Der Monitor belegt die Adressen von 0000 H bis OFFF H und bietet im Bereich von 0C00 H bis 0CFF H frei verfuegbare RAM-Plaetze an.

Die Testbaugruppe wird im Bereich von 0000 H bis OFFF H gesperrt. Dazu wird in die Fassung von D 8 (Adressenvergleicher), ein Test-PROM mit folgendem Inhalt gesteckt:

| Adresse hex. | Inhalt hex. |

|--------------|-------------|

| 00 - 0F      | 00          |

| 10 - FF      | 01          |

Der Steuerflipflop D 14 wird gezogen. Der Ausgang Y1 des PROM's wird fuer die Bauer des Tests mit den Anschluessen 5 und 9 in der Fassung von D 14 verbunden.

Damit ist die Baugruppe fuer den Adressbereich von

0000 H bis OFFF H,

in dem sich der Testmonitor befindet, gesperrt.

Mit Hilfe des Monitors koennen nun zudechst einfache Speicherfunktionen im Adressbereich von 1000 H bis FFFF H getestet werden:

- Mit einem Pruefstift muessen an allen Speicher-IC die Signale /RAS (wegen Refresh), /WE sowie die Daten- und Adresssignale als Impulse nachgewiesen werden koennen.

- Das /CAS-Signal muss auf H-Potential liegen.

- Pruefen, ob alle Datenbits, d. h. alle 8 Speicher-IC der Bank 0 angesprochen werden.

- Fuellen des Speichers mit 1-Byte-Befehlen (z. B. INC HL, 23 H) und nach Programmablauf Kontrolle, ob die entsprechende Anzahl von Erhoebungen des Registers HL erreicht wurden.

- Pruefen, ob Mehrdeutigkeiten bei der Adressierung auftreten, wie sie z.B. durch Kurzzschluessel zwischen Adressleitungen verursacht werden koennen.

- Bei Ausgabeoperationen an die Portadressen (siehe unter 4.4) muessen an den Ausgaengen Y1 bis Y4 T-Signale auftreten.

- Nach den Ausgabeoperationen "LDAH" und "LDBB" muessen an den Ausgaengen der Register D 2 und D 3 die ausgegebenen Daten statisch anliegen.

### 5.2.2.3 Dynamischer Speichertest

Nachdem die in 5.2.2 getesteten Grundfunktionen nachgewie-

sen sind, kann die dynamische Pruefung der Speicherbaugruppe durchgefuehrt werden. Dabei wird kontrolliert, ob ein in der Testbaugruppe gespeichertes Programm im gesamten Adressbereich korrekt abgearbeitet wird.

In der Abteilung R der IH fuer Seefahrt wird dazu ein von LANTOW angegebenes Testprogramm verwendet (Listing siehe in der Anlage). Die Testzeit betraegt ca. 1 s/kByte.

Wird dieses Programm korrekt durchlaufen, so kann diese Testphase beendet werden.

Es folgt der Test des Speichers im gesamten Adressbereich. Dazu muessen die unter 5.2.2 genannten Testbedingungen aufgehoben werden:

- Das Steuerflipflop D 14 wird eingesteckt.

- Die Verbindung von Y1"8 nach 5"14 und 9"14 wird aufgehoben

- Der Test-PROM D 8 wird aus der Fassung entnommen und der Original-PROM D 9 wird eingesteckt.

Die Baugruppe kann nach Aktivierung (Ausgabe der Funktion "Speicher ein") im gesamten Adressraum von 0000 H bis FFFF H beschrieben, jedoch nicht gelesen werden.

Der residente Testmonitor wird von der ROM-Baugruppe in den 256kDRAM kopiert. Danach wird die ROM-Baugruppe abgeschaltet. Dies kann z. B. mit dem folgenden kurzen Programm geschehen:

```

KOPIE: OUT 75H      ; "Speicher ein"

LD  HL, 0000H ; Quelle

LD  DE, 0000H ; Ziel

LD  BC, 1000H ; Anzahl der zu kopierenden Adr.

LDIR

OUT 77H      ; "Lesen freigegeben"

RET

```

Sind die vorhergehenden Tests positiv ausgefallen, so wird nach dem Kopiervorgang in der Regel der Testmonitor in der Testbaugruppe stabil weiterlaufen. Jetzt kann ueber das Fenster auch der eigentliche Floppy-RAM erreicht und getestet werden.

## 6.3 Schaltteilliste

| Nr.                                      | Benennung/Typ/TGL                                                            | ELN.-Nr. (ZAK-Nr.)             | Stueck |

|------------------------------------------|------------------------------------------------------------------------------|--------------------------------|--------|

| <b>....Integrierte Schaltkreise.....</b> |                                                                              |                                |        |

| 1                                        | D16 bis D47<br>U 2164 C25                                                    | TGL 26713 137 87 44 000 216463 | 32     |

| 2                                        | D2, D3, D5, D6, D7<br>DS 8282 D                                              | TGL 42623 137 87 73 004 828216 | 5      |

| 3                                        | D1<br>DS 8286 D                                                              | TGL 42822 137 87 73 004 828654 | 1      |

| 4                                        | D4, D8, D9<br>MH 74 S 287                                                    | CSSR 137 87 73 004 074100      | 3      |

| 5                                        | D13, D14<br>DL 074 D                                                         | TGL 39865 137 87 74 007 074020 | 2      |

| 6                                        | D10<br>DL 008 D                                                              | TGL 39865 137 87 74 007 008031 | 1      |

| 7                                        | D11<br>DL 004 D                                                              | TGL 39865 137 87 74 007 004065 | 1      |

| 8                                        | D12<br>DL 003 D                                                              | TGL 39865 137 87 74 007 003089 | 1      |

| 9                                        | D15<br>DL 000 D                                                              | TGL 39865 137 87 74 007 000128 | 1      |

| 10                                       | R1 bis R8<br>Stromteiler 3845 9 x 4,7 kOhm<br>TGL 29950/01;06 4538.8.4541.86 |                                | 1      |

| 11                                       | R9 bis R14,35<br>330 Ohm                                                     | TGL 8728/01                    | 7      |

| 12                                       | R15 bis R28<br>33 Ohm                                                        | TGL 8728/01                    | 14     |

| 13                                       | R29 bis R34<br>1,2 kOhm                                                      | TGL 8728/01                    | 6      |

| 14                                       | C1 bis C13 Scheibenkondensator 33 nF<br>EBVU-N150 33/10-63 Typ II TGL 35781  |                                | 13     |

| 15                                       | C14 Tantalkondensator<br>22 uF/16 V TGL 38965                                |                                | 1      |

| 16                                       | C15 Scheibenkondensator 2 nF                                                 |                                |        |

256 kByte DRAM/- 25 -

EDVU-n150 2,2/10-63 Typ II TGL 35781

- 17 Bu1 bis Bu3 Fassung 16-polig

DIL P6A 0697 CCSR 6AF49 769

- 18 BU4 Fassung 14-polig

DIL P6A 0697 CCSR 6AF49 770

- 19 St 1 Steckerleiste, 58-polig

TGL 29331/03 137 73 32 47

## Logische Adresse des Rechners

Physische Adresse des Speichers

außerhalb des Fensters

logischer und phys. Teil immer gleich

- a) Multiprogramm-Betrieb

logische Adresse außerhalb des Fensters

akt.  $b_1$   $b_\emptyset$  A15      A8 A7      A $\emptyset$

logische Adresse innerhalb des Fensters

akt. B<sub>1</sub> B<sub>0</sub> A 15 A 8 A 7 A 0

- b) Hauptspeicher und 192-k-RAM-Floppy

logische Adresse außerhalb des Fensters

akt.  $b_1$   $b_g$  A15 A8 A7 AØ

logische Adresse innerhalb des Fensters

akt. B<sub>1</sub> B<sub>2</sub> A 15\* A 8\* A 7 A Ø

- c) 256-k-RAM -Floppy

logische Adresse außerhalb des Fensters (Speicher inaktiv)

inakt. X X X X X X X X X A? AØ

- d) logische Adresse innerhalb des Fensters (Speicher aktiv)

Bild 1

### Betriebsarten der Baugruppe

Bild 2

\*) schematische Darstellung

Bild 3

Bild 4

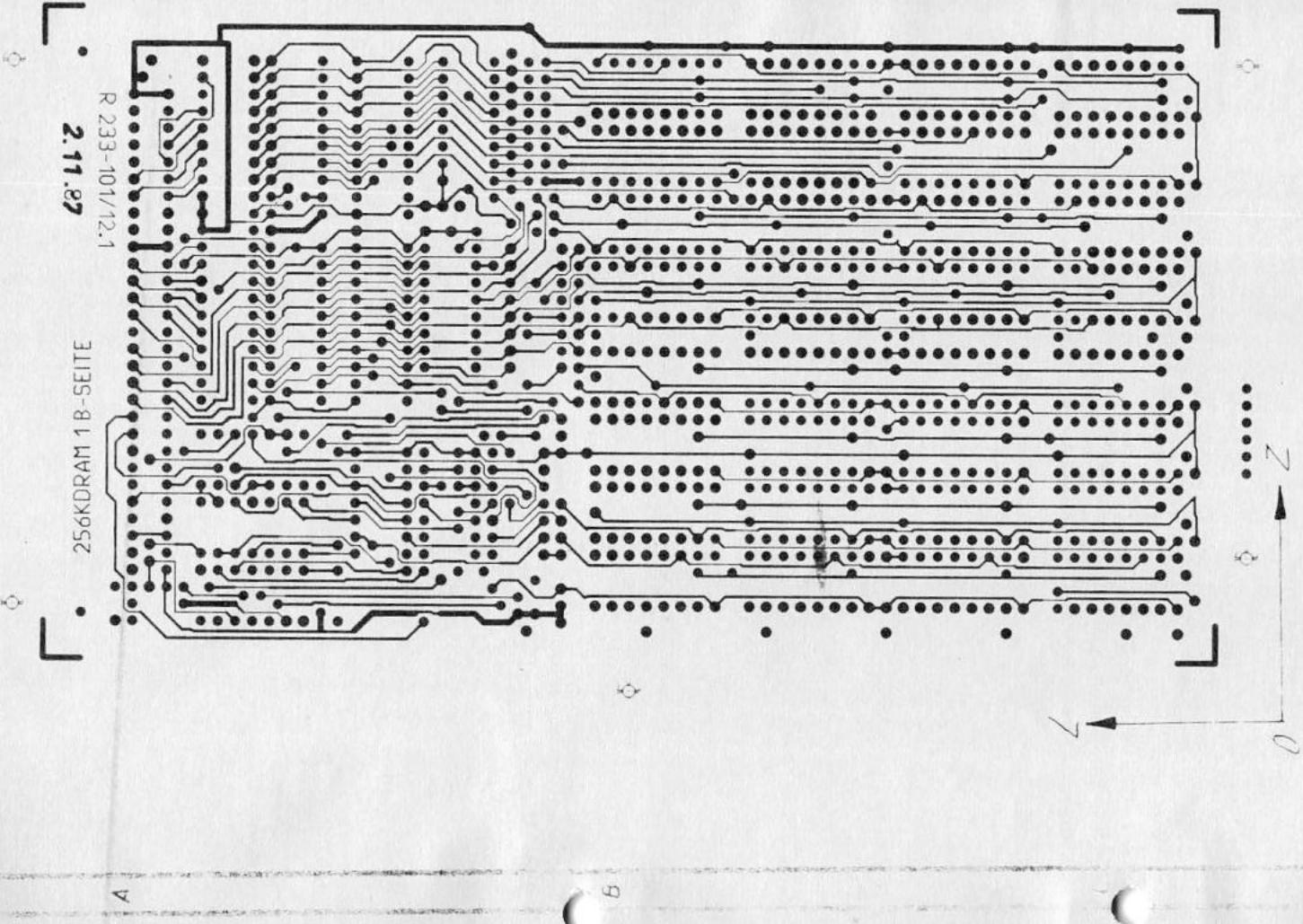

R 233-101/12.1

Bl. 29

|           |        |       |      |                    |

|-----------|--------|-------|------|--------------------|

| 1987      | Montag | Datum | Name | Zeichnung-Nr.      |

| Seite:    |        | 23.3. | Kü   | R 233 - 101 / 12.1 |

| Zeichner: |        |       |      | 1HS                |

| Prüfer:   |        |       |      | Hornemünde         |

|           |        |       |      |                    |

Leiterplatte

Leiterbildzeichnung B

IGL 25016/02

Maßstab 1:1

Zeichnung für Maßnahmen und Anordnungen

Gezeichnet am 23.3.1987 durch

TKO Gepr.: für

(95 x 170)

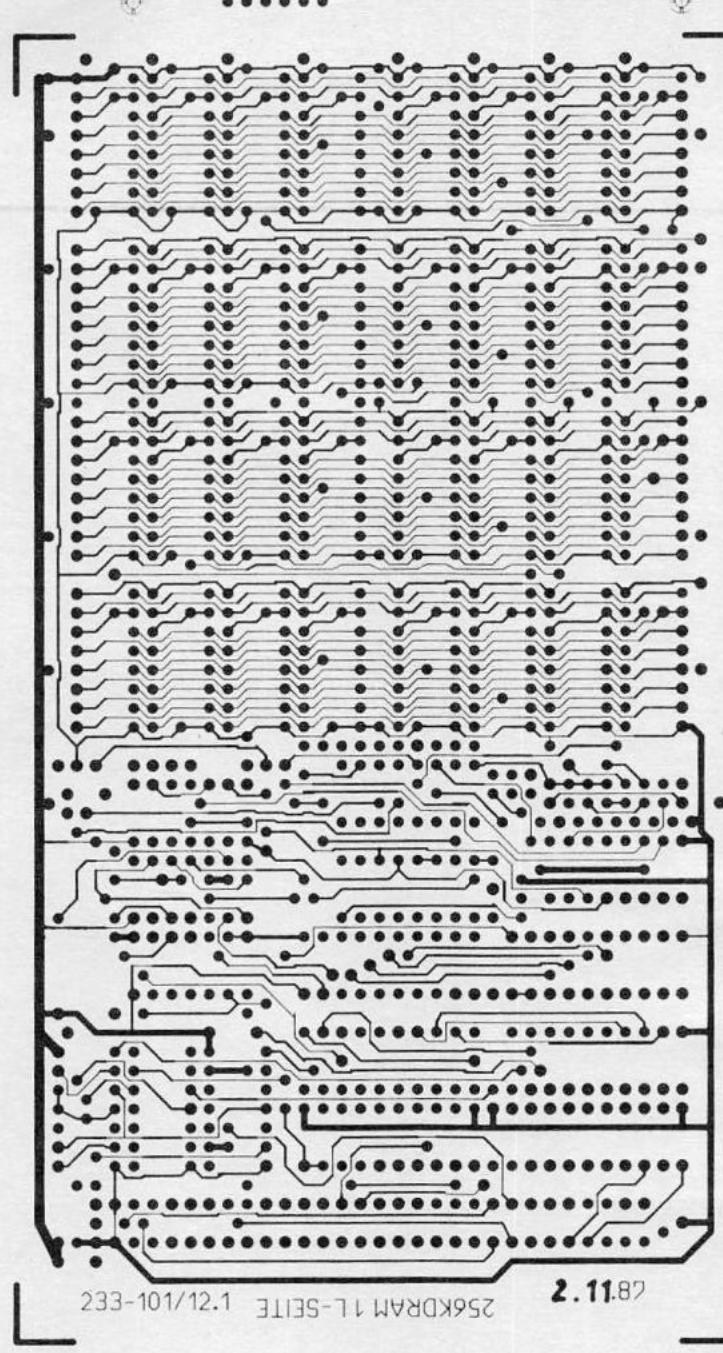

|                              |            |       |                                                |                                       |

|------------------------------|------------|-------|------------------------------------------------|---------------------------------------|

|                              |            |       | Halbzeug/Werkstoff                             | zur Abw. für Maße<br>ohne Vorlaufrand |

|                              |            |       |                                                | TGL 25016/102                         |

| D                            |            |       | Gehäuse: Leiterplatte<br>Leiterbildzeichnung L | Maßstab: 1:1                          |

| AZ                           | Mitteilung | Datum | Name                                           | Maßstab: 1:1                          |

| 1987                         | Datum      | Name  | Zeichnungs-Nr.                                 | Maßstab:                              |

| Bearb.<br>Kunst/<br>Technik. | 23.3.      | KU    | R 233 - 101/12.1 L                             | IHS                                   |

| Stand                        |            |       |                                                | Wornemünde                            |

|                              |            |       | Ers. für                                       | tra durch                             |